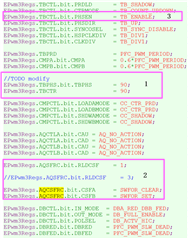

如下图所示为我们Epwm3模块的配置。我们在配置EPWM模块之前会设置CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;,配置完成后设置CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; 初始配置时通过

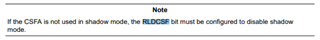

EPwm3Regs.AQSFRC.bit.RLDCSF = 1; /* Load when counter=PRD */

EPwm3Regs.AQCSFRC.bit.CSFA = SWFOR_CLEAR;

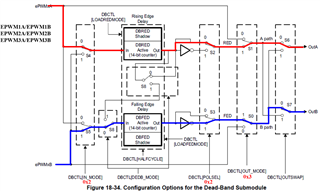

EPwm3Regs.AQCSFRC.bit.CSFB = SWFOR_SET;来实现EPWM3A和EPWM3B输出低电平。但是实际测试时发现EPWM3A为低电平,EPWM3B始终为高电平,并且在后面的应用程序中继续操作CSFA和CSFB也无法实现输出电平变化。此时若将图中2处, EPwm3Regs.AQSFRC.bit.RLDCSF = 1; /* Load when counter=PRD * /改为 EPwm3Regs.AQSFRC.bit.RLDCSF = 3; /* Load immediately * /,则EPWM3A和EPWM3B初始电平就可以都为低电平。若保持EPwm3Regs.AQSFRC.bit.RLDCSF = 1不变,将图上1处的TBPHS或者TBCTR改为0,或者将3处的PHSEN改为0,则驱动也是正常的。麻烦专家们帮忙看一下时什么原因?看起来像是时钟相关问题导致SW forced event失效?