Other Parts Discussed in Thread: C2000WARE

采用增减计数模式时,看技术手册里只能在CAU或CAD时产生ADC的触发信号,有没有什么其他的办法能实现在递增和递减的时候都在CMPA处产生触发?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

采用增减计数模式时,看技术手册里只能在CAU或CAD时产生ADC的触发信号,有没有什么其他的办法能实现在递增和递减的时候都在CMPA处产生触发?

如果是一个PWM的没办法触发两次ADC。但是可以配置两个PWM模块,PWM1在递增的CMPA处输出触发信号,PWM2在递减的CMPA处输出触发信号。

这个配置SOC触发同一个ADC就可以了。

例程也可以参考一下:C:\ti\c2000\C2000Ware_4_01_00_00\device_support\f2803x\examples\c28\adc_soc

是要同时对一个周期的两个采样值做处理,还是单个做处理就可以了?

如果是前者,那定义两个变量就可以了,这个比较简单。

如果是后者,只定义一个变量的话需要确保计算完成之前变量的值没有更新,也就是结果寄存器的值没有更新。也就是要在下一次采样完成前完成计算。不过如果你的计算不复杂的话应该几乎不会有什么问题。

你好,3处应该是ADCRESULT1的值了吧?

前面说用两个PWM去触发ADC的时候忘了说可以加上一个PWM同步,也就是将PWM2跟PWM1进行同步。这样的话3就不可能被2覆盖,只可能2被3覆盖。

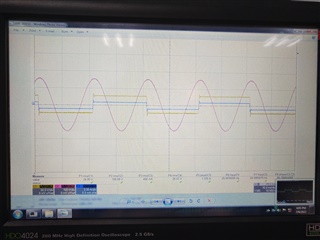

我用这样的方法,但是好像一个周期只采到了一次,能麻烦您看一下这个程序这样有什么问题吗?

EPwm1Regs.TBCTL.bit.CTRMODE =2; // 增减计数

EPwm1Regs.TBCTL.bit.PHSEN = 0; // 禁止相位加载

EPwm1Regs.TBCTL.bit.HSPCLKDIV =0; // 高速外设时钟基准分频系数

EPwm1Regs.TBCTL.bit.CLKDIV = 1; // 时间基准时钟分频,TBCLK=SYSCLK/(HSPCLKDIV*CLKDIV)

EPwm1Regs.TBCTL.bit.SYNCOSEL=TB_CTR_ZERO;

//设置周期寄存器,计数器清零

EPwm1Regs.TBPRD =1000; // 载波频率 30M/(2*1000)=15kHz

EPwm1Regs.TBPHS.half.TBPHS = 0; // 相位设为0

EPwm1Regs.TBCTR = 0; // 初始化计数器

// 设置比较寄存器

EPwm1Regs.CMPA.half.CMPA = 500; // CMPA初始为最小占空比

//设置寄存器映射

EPwm1Regs.CMPCTL.bit.SHDWAMODE = 0; // 使能映射

EPwm1Regs.CMPCTL.bit.LOADAMODE = 2; // 计数器为 zero 或者 PRD 时加载映射寄存器

// 设置比较匹配后有效电平

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; // 1:输出高电平;2:输出高电平

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; // 周期匹配时置为低电平

/*死区时间设置1us*/

EPwm1Regs.DBCTL.bit.IN_MODE = 0;

EPwm1Regs.DBCTL.bit.POLSEL = 2;

EPwm1Regs.DBCTL.bit.OUT_MODE = 3;

EPwm1Regs.DBRED = 10;

EPwm1Regs.DBFED = 10;

EPwm1Regs.ETSEL.bit.SOCAEN= 1; // Enable SOC on A group, Enable EPWMxSOCA pulse.

EPwm1Regs.ETSEL.bit.SOCASEL= 4; // Enable event time-base counter equal to CMPA when the timer is incrementing.

EPwm1Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

EPwm1Regs.ETSEL.bit.SOCBEN = 1; // Enable SOC on B group, Enable EPWMxSOCB pulse.

EPwm1Regs.ETSEL.bit.SOCBSEL = 5; // Enable event time-base counter equal to CMPA when the timer is decrementing.

EPwm1Regs.ETPS.bit.SOCBPRD = 1; // Generate pulse on 1st event

EPwm1Regs.ETSEL.bit.INTEN = 0; // 禁止中断

/*ADC采样通道设置*/

AdcRegs.ADCSOC10CTL.bit.CHSEL = 0x0A; //ADCINB2,转换结果ADCRESULT10

AdcRegs.ADCSOC10CTL.bit.TRIGSEL = 0x05; //set SOC10 start trigger on EPWM1A

AdcRegs.ADCSOC10CTL.bit.ACQPS = 0x06; //set SOC10 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

AdcRegs.ADCSOC11CTL.bit.CHSEL = 0x0A; //ADCINB2,转换结果ADCRESULT11

AdcRegs.ADCSOC11CTL.bit.TRIGSEL = 0x06; //set SOC11 start trigger on EPWM1B

AdcRegs.ADCSOC11CTL.bit.ACQPS = 0x06; //set SOC11 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

ILf2Cur1 = AdcResult.ADCRESULT10;

ILf2Cur1 = AdcResult.ADCRESULT11;

ILf2Cur = -_IQmpy(_IQ12toIQ(ILf2Cur1),_IQ(3.3))+_IQ(1.5909);