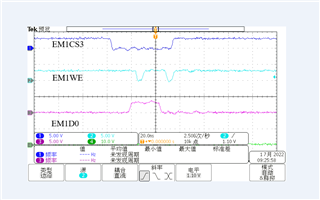

根据emif1_16bit_asram.c修改,配置EMIF模块,在写的过程中EMIWE被拉低两次。这是怎么回事。

代码如下:

//###########################################################################

//

// FILE: emif1_16bit_asram.c

//

// TITLE: EMIF1 module accessing 16bit ASRAM.

//

//! \addtogroup cpu01_example_list

//! <h1> EMIF ASYNC module (emif1_16bit_asram)</h1>

//!

//! This example configures EMIF1 in 16bit ASYNC mode

//! This example uses CS2 as chip enable.

//!

//! \b Watch \b Variables: \n

//! - \b TEST_STATUS - Equivalent to \b TEST_PASS if test finished correctly,

//! else the value is set to \b TEST_FAIL

//! - \b ErrCount - Error counter

//!

//

//###########################################################################

//

// $Release Date: $

// $Copyright:

// Copyright (C) 2013-2022 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

//

// Included Files

//

#include "F28x_Project.h"

#define ASRAM_CS2_START_ADDR 0x100000

#define ASRAM_CS2_SIZE 0x8000

//

// Globals

//

Uint16 ErrCount = 0;

Uint32 TEST_STATUS;

int i;

//

// Function Prototypes

//

extern void setup_emif1_pinmux_async_16bit(Uint16);

// mem_read_write - This function performs simple read/write word accesses to memory.

char mem_read_write(Uint32 start_addr, Uint32 mem_size)

{

//unsigned long mem_rds;

unsigned long mem_wds;

long *XMEM_ps;

//unsigned int i;

//Write data

XMEM_ps = (long *)start_addr;

//Fill memory

mem_wds = 0x1;

//for (i=0; i < mem_size; i++)

//{

//*XMEM_ps++ = mem_wds;

*XMEM_ps = mem_wds;

// mem_wds += 0x11111111;

//}

/*

//Verify memory

mem_wds = 0x01234567;

XMEM_ps = (long *)start_addr;

for (i=0; i < mem_size; i++)

{

mem_rds = *XMEM_ps;

if( mem_rds != mem_wds)

{

return(1);

}

XMEM_ps++;

mem_wds += 0x11111111;

}

*/

return(0);

}

void main(void)

{

char ErrCount_local;

//TEST_STATUS = TEST_FAIL;

//

// Initialize system control

//

InitSysCtrl();

DINT;

//

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the F2837xD_PieCtrl.c file.

//

InitPieCtrl();

//

// Disable CPU interrupts and clear all CPU interrupt flags:

//

EALLOW;

IER = 0x0000;

IFR = 0x0000;

EDIS;

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// GService Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in F2837xD_DefaultIsr.c.

// This function is found in F2837xD_PieVect.c.

//

InitPieVectTable();

//

//Configure to run EMIF1 on full Rate (EMIF1CLK = CPU1SYSCLK)

//

EALLOW;

ClkCfgRegs.PERCLKDIVSEL.bit.EMIF1CLKDIV = 0x0;

EDIS;

EALLOW;

//

// Grab EMIF1 For CPU1

//

Emif1ConfigRegs.EMIF1MSEL.all = 0x93A5CE71;

if(Emif1ConfigRegs.EMIF1MSEL.all != 0x1)

{

ErrCount++;

}

//

//Disable Access Protection (CPU_FETCH/CPU_WR/DMA_WR)

//

Emif1ConfigRegs.EMIF1ACCPROT0.all = 0x0;

if(Emif1ConfigRegs.EMIF1ACCPROT0.all != 0x0)

{

ErrCount++;

}

//

// Commit the configuration related to protection. Till this bit remains set

// content of EMIF1ACCPROT0 register can't be changed.

//

Emif1ConfigRegs.EMIF1COMMIT.all = 0x1;

if(Emif1ConfigRegs.EMIF1COMMIT.all != 0x1)

{

ErrCount++;

}

//

// Lock the configuration so that EMIF1COMMIT register can't be

// changed any more.

//

Emif1ConfigRegs.EMIF1LOCK.all = 0x1;

if(Emif1ConfigRegs.EMIF1LOCK.all != 1)

{

ErrCount++;

}

EDIS;

EALLOW;

GpioCtrlRegs.GPBDIR.bit.GPIO32 = 1;//配置方向:0输入;1输出

GpioCtrlRegs.GPBDIR.bit.GPIO33 = 1;

GpioCtrlRegs.GPBPUD.bit.GPIO32 = 0;//上拉:0使能上拉;1禁止上拉

GpioCtrlRegs.GPBPUD.bit.GPIO33 = 0;

GpioDataRegs.GPBCLEAR.bit.GPIO32 = 1;//数据清除:写0无效;写1置为低电平

GpioDataRegs.GPBCLEAR.bit.GPIO33 = 1;//数据清除:写0无效;写1置为低电平

EDIS;

//

//Configure GPIO pins for EMIF1

//

setup_emif1_pinmux_async_16bit(0);

Emif1Regs.ASYNC_CS2_CR.bit.ASIZE = 1;//1:0

Emif1Regs.ASYNC_CS2_CR.bit.TA= 10; //3:2

//Emif1Regs.ASYNC_CS2_CR.bit.R_HOLD= 0;//6:4

//Emif1Regs.ASYNC_CS2_CR.bit.R_STROBE = 0;//12:7

//Emif1Regs.ASYNC_CS2_CR.bit.R_SETUP = 0;//16:13

Emif1Regs.ASYNC_CS2_CR.bit.W_HOLD =0;//19:17

Emif1Regs.ASYNC_CS2_CR.bit.W_STROBE =2;//25:20

Emif1Regs.ASYNC_CS2_CR.bit.W_SETUP =0;//29:26

Emif1Regs.ASYNC_CS2_CR.bit.EW = 0;//30

Emif1Regs.ASYNC_CS2_CR.bit.SS = 0;//31

while (1)

{

ErrCount_local = mem_read_write(ASRAM_CS2_START_ADDR, ASRAM_CS2_SIZE);

ErrCount = ErrCount + ErrCount_local;

DELAY_US(100);

}

}