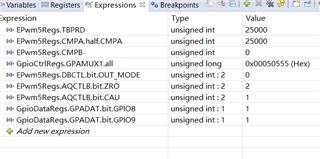

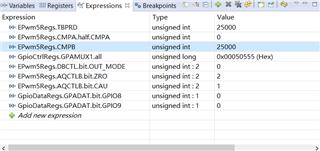

配置如下: GPIO 8和9 也配置了PWMA PWMB功能, 实际测试PWMB输出占空比一直和A一样,是否配置有问题

#define PWM_DA_PRD (PWM_PERIOD*2 / 6) // 6K UP MODE need *2

#define PWM_DA_CH EPwm5Regs

volatile struct EPWM_REGS *EPwmRegs;

WORD wPeriod = PWM_DA_PRD;

EPwmRegs = (struct EPWM_REGS *)((WORD *)&PWM_DA_CH.TBCTL.all);

EPwmRegs->TBPRD = PWM_DA_PRD; // DA 6k

EPwmRegs->CMPA.half.CMPA = (float)PWM_DA_PRD* 0.2f;

EPwmRegs->CMPB = (float)PWM_DA_PRD * 0.6f;

EPwmRegs->TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwmRegs->TBCTR = 0x0000; // Clear counter

EPwmRegs->TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwmRegs->TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwmRegs->TBCTL.bit.PRDLD = TB_SHADOW;

EPwmRegs->TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;

#ifdef CLK_150MTBCLK

EPwmRegs->TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwmRegs->TBCTL.bit.CLKDIV = TB_DIV1;

#else

EPwmRegs->TBCTL.bit.HSPCLKDIV = TB_DIV2; // Clock ratio to SYSCLKOUT

EPwmRegs->TBCTL.bit.CLKDIV = TB_DIV1;

#endif

EPwmRegs->CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwmRegs->CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwmRegs->CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwmRegs->CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Setup compare

EPwmRegs->DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwmRegs->AQCTLA.bit.ZRO = AQ_SET;

EPwmRegs->AQCTLA.bit.CAU = AQ_CLEAR;

EPwmRegs->AQCTLB.bit.ZRO = AQ_SET;

EPwmRegs->AQCTLB.bit.CAU = AQ_CLEAR;

极端配置比较值然后看 GPIO 8 9 也是类似现象