Part Number: TMS320F28374S

各位大侠:

当前在设置采样时,发现如果同一路采样例如ADCA,在配置SOC过程中,采用了时钟不同步,频率不相同的不同EPWM触发源,会非常大概率存在采样异常情况,想请问一下,当这种情况下,需要注意些什么,采用外部电路都是运放输入的,

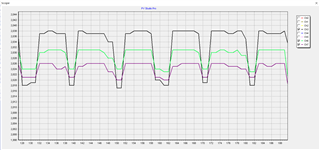

具体配置附件,附件影响ADC采样的就是触发源0x0F,EPWM6,因为他的同步时钟已经和其他EPWM不一样( EPwm6Regs.TBCTL.bit.PHSEN= TB_DISABLE;),频率为31K,与其他几路EPWM不同步,EPWM3/EPWM4=30K,和EPWM1/2同步,ADC异常采样见附件。

/**********************************ADC配置*********************************************/

/*ADC Clock Prescaler, Sys CLock = 200M, ADC Clock = 200/4 = 50M*/

/*TODO:>set 6 ADCCLK divider to /4, 50M*/

/*TODO:>set 2 ADCCLK divider to /2, 100M*/

AdcaRegs.ADCCTL2.bit.PRESCALE = 2;

AdcbRegs.ADCCTL2.bit.PRESCALE = 2;

AdccRegs.ADCCTL2.bit.PRESCALE = 2;

AdcdRegs.ADCCTL2.bit.PRESCALE = 2;

/*SOC Signaling Mode*/

AdcSetMode(ADC_ADCA, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

AdcSetMode(ADC_ADCB, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

AdcSetMode(ADC_ADCC, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

AdcSetMode(ADC_ADCD, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

/*Set pulse positions to late*/

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdcbRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdccRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdcdRegs.ADCCTL1.bit.INTPULSEPOS = 1;

/*power up the ADC*/

/*0-All analog circuitry inside the core is powered down*/

/*1-All analog circuitry inside the core is powered up*/

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1;

AdcbRegs.ADCCTL1.bit.ADCPWDNZ = 1;

AdccRegs.ADCCTL1.bit.ADCPWDNZ = 1;

AdcdRegs.ADCCTL1.bit.ADCPWDNZ = 1;

/*ADC interruput 1 enable*/

/*0-ADCINTFLG register is cleared, ADCINT2 pulses are generated*/

/*1-ADCINT2 pulses are generated whenever an EOC pulse is generated*/

AdcaRegs.ADCINTSEL1N2.bit.INT1CONT = 1; //连续模式

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; //Int Enable

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0x05;//EOC5 is trigger for ADCINT1

/*ADC interruput 2 enable*/

AdcbRegs.ADCINTSEL1N2.bit.INT1CONT = 1; //连续模式

AdcbRegs.ADCINTSEL1N2.bit.INT1E = 1; //Int Enable

AdcbRegs.ADCINTSEL1N2.bit.INT1SEL = 0x01;//EOC1 is trigger for ADCINT1

//delay for 1ms to allow ADC time to power up

DELAY_US(1000);

/*TODO:>采样窗口最小14,5ns*20 = 100ns*/

/* Sample ADCINA1 PV1_I, triggered by eMPW6 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 1;

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 0x0F;

AdcaRegs.ADCSOC0CTL.bit.ACQPS = 19;

/* Sample ADCINA3 PV2_I, triggered by eMPW7 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC1CTL.bit.CHSEL = 3;

AdcaRegs.ADCSOC1CTL.bit.TRIGSEL = 0x11;

AdcaRegs.ADCSOC1CTL.bit.ACQPS = 19;

/* Sample ADCINA5 BAT1_I, triggered by eMPW3 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC2CTL.bit.CHSEL = 5;

AdcaRegs.ADCSOC2CTL.bit.TRIGSEL = 0x09;

AdcaRegs.ADCSOC2CTL.bit.ACQPS = 19;

/* Sample ADCINA0 PV1_VOLT Voltage, triggered by eMPW1 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC3CTL.bit.CHSEL = 0;

AdcaRegs.ADCSOC3CTL.bit.TRIGSEL = 0x05;

AdcaRegs.ADCSOC3CTL.bit.ACQPS = 19;

/* Sample ADCINA2 PV2_VOLT Voltage, triggered by eMPW1 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC4CTL.bit.CHSEL = 2;

AdcaRegs.ADCSOC4CTL.bit.TRIGSEL = 0x05;

AdcaRegs.ADCSOC4CTL.bit.ACQPS = 19;

/* Sample ADCINA4 BAT_VOLT, triggered by eMPW1 ADCSOCA, 12 system clock smaple window */

AdcaRegs.ADCSOC5CTL.bit.CHSEL = 4;

AdcaRegs.ADCSOC5CTL.bit.TRIGSEL = 0x05;

AdcaRegs.ADCSOC5CTL.bit.ACQPS = 19;

/**********************************EPWM配置*****************************************************************************************/

{

EALLOW;

InputXbarRegs.INPUT1SELECT = 29;//DC_OCP - GPIO29 - TZ1

InputXbarRegs.INPUT2SELECT = 31;//INV_OCP - GPIO31 - TZ2

InputXbarRegs.INPUT3SELECT = 99;//BUS_OVP - GPIO99 - TZ3

EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Stop all the TB clocks

ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 1;// EPWMCLK必须2分频SYSCLK

EDIS;

//RLDCSF - AQSFRC寄存器中的值从阴影寄存器中的载入方式,零点载入,周期值载入还是立即载入

//EPwm1Regs.AQSFRC.bit.RLDCSF = 0x03; // load immediately

//EPwm2Regs.AQSFRC.bit.RLDCSF = 0x03; // load immediately

// force all PWM to low

// AQCSFRC - CSFB + CSFA

// CSFB + CSFA

// 00 00 - disable

// 01 01 - B low & A low

// 10 10 - B high & A high

// 11 11 - disable

// EPwm1Regs.AQCSFRC.all = 0x05; // 0101, A low & B low

// EPwm2Regs.AQCSFRC.all = 0x05; // 0101, A low & B low

//时钟输入均默认PWM1的时钟

//EPWM1->EPWM2->EPWM3

//EPWM1->EPWM4->EPWM5-EPWM6

//EPWM1->EPWM7->EPWM8-EPWM9

//EPWM1->EPWM10->EPWM11-EPWM12

/* inverter ePWM generator */

//================================================================================

//PWM1A-G1和G4在正半周期发出相同的PWM波

//PWM1B-G6在正半周期发出互补的PWM波

//PWM2A-G2和G3在负半周期发出相同的PWM波

//PWM2B-G5在负半周期发出互补的PWM波

EPwm1Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm1Regs.TBPRD = INV_PWM_PERD; //set the PWM period

EPwm1Regs.TBPHS.bit.TBPHS = 2;

EPwm1Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //Master, Sent sync signal while count to zero

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; //Master, no need phase load

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm1Regs.TBCTR = 0;

EPwm1Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm1Regs.CMPB.bit.CMPB = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; //Load compare A register when counter = zero or period

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; //Load compare B register when counter = zero or period

//比较点的动作

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm1Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm1Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

//死区设置

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //enable inverter PWM deadband control

EPwm1Regs.DBRED.bit.DBRED = DB_1US;

EPwm1Regs.DBFED.bit.DBFED = DB_1US;

EPwm1Regs.ETSEL.bit.SOCAEN = 1; //Enable PWM1SOCA

EPwm1Regs.CMPB.bit.CMPB = 250;

EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = comapre B

EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

//触发TZ时的设置-TODO-放到死区的前面

EPwm1Regs.TZSEL.bit.OSHT1 = TZ_ENABLE; //PV过流

EPwm1Regs.TZSEL.bit.OSHT2 = TZ_ENABLE; //逆变过流

EPwm1Regs.TZSEL.bit.OSHT3 = TZ_ENABLE; //电池过流

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; //触发TZ时输出低电平

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm1Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

//PWM1触发中断设置

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; //Interrupt when counter = zero

EPwm1Regs.ETPS.bit.INTPRD = ET_1ST; //Interrupt generate on the first time

EPwm1Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

/* inverter ePWM generator */

EPwm2Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm2Regs.TBPRD = INV_PWM_PERD; //set the PWM period

EPwm2Regs.TBPHS.bit.TBPHS = 2;

EPwm2Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //Sent sync signal while count to zero

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; //

EPwm2Regs.TBCTL.bit.PHSDIR = 1;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm2Regs.TBCTR = 0;

EPwm2Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm2Regs.CMPB.bit.CMPB = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; //Load compare A register when counter = zero or period

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; //Load compare B register when counter = zero or period

//比较点的动作

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm2Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm2Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm2Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

//死区设置

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //enable inverter PWM deadband control

EPwm2Regs.DBRED.bit.DBRED = DB_1US;

EPwm2Regs.DBFED.bit.DBFED = DB_1US;

EPwm2Regs.ETSEL.bit.SOCAEN = 1; //Disable PWM2SOCA

EPwm2Regs.CMPB.bit.CMPB = 250;

EPwm2Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = comapre B

EPwm2Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

EPwm2Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT2 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT3 = TZ_ENABLE;

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm2Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

//PWM2触发中断的设置

EPwm2Regs.ETSEL.bit.INTSEL = ET_CTR_PRDZERO; //Interrupt when counter = zero or period

EPwm2Regs.ETPS.bit.INTPRD = ET_1ST; //Interrupt generate on the first time

EPwm2Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

//--------------------------------------------------------------------------------

/*Charger ePWM generator, Buck-Boost*/

EPwm3Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm3Regs.TBPRD = BAT_PWM_PERD; //set the PWM period

EPwm3Regs.TBPHS.bit.TBPHS = 2;

EPwm3Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm3Regs.TBCTL.bit.PHSDIR = 1;

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm3Regs.TBCTR = 0;

EPwm3Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm3Regs.CMPB.bit.CMPB = 0;

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; //Load compare A register when counter = zero or period

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; //Load compare B register when counter = zero or period

EPwm3Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm3Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm3Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm3Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

EPwm3Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable inverter PWM deadband control

EPwm3Regs.DBRED.bit.DBRED = DB_1US;

EPwm3Regs.DBFED.bit.DBFED = DB_1US;

EPwm3Regs.ETSEL.bit.SOCAEN = 1; //Disable PWM1SOCA

EPwm3Regs.CMPB.bit.CMPB = 300;

EPwm3Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = compare B

EPwm3Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

EPwm3Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT2 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT3 = TZ_ENABLE;

EPwm3Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm3Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

EPwm3Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

/*Charger ePWM generator, Buck-Boost*/

EPwm4Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm4Regs.TBPRD = BAT_PWM_PERD; //set the PWM period

EPwm4Regs.TBPHS.bit.TBPHS = BAT_PWM_PERD;

EPwm4Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm4Regs.TBCTL.bit.PHSDIR = 1;

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm4Regs.TBCTR = 0;

EPwm4Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm4Regs.CMPB.bit.CMPB = 0;

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; //Load compare A register when counter = zero or period

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; //Load compare B register when counter = zero or period

EPwm4Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm4Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm4Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm4Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

EPwm4Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable inverter PWM deadband control

EPwm4Regs.DBRED.bit.DBRED = DB_1US;

EPwm4Regs.DBFED.bit.DBFED = DB_1US;

EPwm4Regs.ETSEL.bit.SOCAEN = 1; //Disable PWM1SOCA

EPwm4Regs.CMPB.bit.CMPB = 300;

EPwm4Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = compare B

EPwm4Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

EPwm4Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT2 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT3 = TZ_ENABLE;

EPwm4Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm4Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

EPwm4Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

/*PWM5-NoUsed*/

EPwm5Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm5Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

//--------------------------------------------------------------------------------

/*Boost1 ePWM generator*/

EPwm6Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm6Regs.TBPRD = BOOST_PWM_PERD; // set the PWM period

EPwm6Regs.TBPHS.bit.TBPHS = 2;

EPwm6Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm6Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm6Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm6Regs.TBCTL.bit.PHSEN = TB_DISABLE;

EPwm6Regs.TBCTL.bit.PHSDIR = 1;

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm6Regs.TBCTR = 0;

EPwm6Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm6Regs.CMPB.bit.CMPB = 0;

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_PRD; //Load compare A register when counter = zero or period

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_PRD; //Load compare B register when counter = zero or period

EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm6Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm6Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm6Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

EPwm6Regs.ETSEL.bit.SOCAEN = 1; //enable PWM7SOCA

EPwm6Regs.CMPB.bit.CMPB = 50;

EPwm6Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = compare B

EPwm6Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

EPwm6Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm6Regs.TZSEL.bit.OSHT2 = TZ_ENABLE;

EPwm6Regs.TZSEL.bit.OSHT3 = TZ_ENABLE;

EPwm6Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm6Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm6Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

EPwm6Regs.ETSEL.bit.INTSEL = ET_CTR_PRDZERO; //Interrupt when counter = zero or period

EPwm6Regs.ETPS.bit.INTPRD = ET_1ST; //Interrupt generate on the first time

EPwm6Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

/* Boost2 ePWM generator */

EPwm7Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm7Regs.TBPRD = BOOST_PWM_PERD; //set the PWM period

EPwm7Regs.TBPHS.bit.TBPHS = BOOST_PWM_PERD;

EPwm7Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm7Regs.TBCTL.bit.PHSDIR = 1;

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm7Regs.TBCTR = 0;

EPwm7Regs.CMPA.bit.CMPA = 0; //Duty = 0% at the beginning

EPwm7Regs.CMPB.bit.CMPB = 0;

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_PRD; //Load compare A register when counter = zero or period

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_PRD; //Load compare B register when counter = zero or period

EPwm7Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm7Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm7Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm7Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

EPwm7Regs.ETSEL.bit.SOCAEN = 1; //enable PWMxSOCA

EPwm7Regs.CMPB.bit.CMPB = 50;

EPwm7Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = compare B

EPwm7Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EALLOW;

EPwm7Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm7Regs.TZSEL.bit.OSHT2 = TZ_ENABLE;

EPwm7Regs.TZSEL.bit.OSHT3 = TZ_ENABLE;

EPwm7Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm7Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm7Regs.TZFRC.bit.OST = 1; //Disable PWM at first

EDIS;

EPwm7Regs.ETSEL.bit.INTSEL = ET_CTR_PRDZERO; //Interrupt when counter = zero or period

EPwm7Regs.ETPS.bit.INTPRD = ET_1ST; //Interrupt generate on the first time

EPwm7Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

//--------------------------------------------------------------------------------

/*********************32K倍频---EPWM配置作为ADC触发使用->逆变器电压电流*********************/

EALLOW;

SyncSocRegs.SYNCSELECT.bit.EPWM10SYNCIN = 0; //时钟同步到EPWM1->INV

EDIS;

EPwm10Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm10Regs.TBPRD = INV_PWM_PERD>>1; //set the PWM period

EPwm10Regs.TBPHS.bit.TBPHS = 0;

EPwm10Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm10Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm10Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm10Regs.TBCTL.bit.PHSEN = TB_ENABLE; //Master, no need phase load

EPwm10Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm10Regs.TBCTR = 0;

EPwm10Regs.CMPA.bit.CMPA = INV_PWM_PERD>>2; //Duty = 0% at the beginning

EPwm10Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm10Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm10Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; //Load compare A register when counter = zero or period

EPwm10Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; //Load compare B register when counter = zero or period

//比较点的动作

EPwm10Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm10Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm10Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm10Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

//TEST-EPWM10A开波,保证EPWM10触发和逆变器发波时钟一致:

//死区设置

EPwm10Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm10Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm10Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //enable inverter PWM deadband control

EPwm10Regs.DBRED.bit.DBRED = DB_1US;

EPwm10Regs.DBFED.bit.DBFED = DB_1US;

EPwm10Regs.ETSEL.bit.SOCAEN = 1; //Enable PWM10SOCA

EPwm10Regs.CMPB.bit.CMPB = 250;

EPwm10Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPB; //Enable event time-base counter count up and = comapre B

EPwm10Regs.ETPS.bit.SOCAPRD = ET_1ST; //Generate the EPWMxSOCA pulse on the first event

EPwm10Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; //Interrupt when counter = zero

EPwm10Regs.ETPS.bit.INTPRD = ET_1ST; //Interrupt generate on the first time

EPwm10Regs.ETSEL.bit.INTEN = ET_DISABLE; //disable PWM interrupt

//--------------------------------------------------------------------------------

/*驱动电源的PWM-Driver power ePWM generator*/

EPwm11Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE;

EPwm11Regs.TBPRD = DRV_PWM_PERD; //set the PWM period

EPwm11Regs.TBPHS.bit.TBPHS = 2;

EPwm11Regs.TBCTL.bit.FREE_SOFT = 2; //Free run

EPwm11Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm11Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //TBCLK = SYS_CLK/(CLKDIV * HSPCLKDIV)

EPwm11Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm11Regs.TBCTL.bit.PHSEN = TB_DISABLE; //独立主机不载入相位

EPwm11Regs.TBCTL.bit.PHSDIR = 1;

EPwm11Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //Count up down mode

EPwm11Regs.TBCTR = 0;

EPwm11Regs.CMPA.bit.CMPA = EPwm11Regs.TBPRD>>1;

EPwm11Regs.CMPB.bit.CMPB = 0;

EPwm11Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; //Using shadow

EPwm11Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; //Using shadow

EPwm11Regs.CMPCTL.bit.LOADAMODE = CC_CTR_PRD; //Load compare A register when counter = zero or period

EPwm11Regs.CMPCTL.bit.LOADBMODE = CC_CTR_PRD; //Load compare B register when counter = zero or period

EPwm11Regs.AQCTLA.bit.CAU = AQ_CLEAR; //Force 0 when counter count up and = compare A

EPwm11Regs.AQCTLA.bit.CAD = AQ_SET; //Force 1 when counter count down and = compare A

EPwm11Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; //Do nothing at equal to zero

EPwm11Regs.AQCTLA.bit.PRD = AQ_NO_ACTION; //Do nothing at period

EPwm11Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm11Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm11Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable inverter PWM deadband control

EPwm11Regs.DBRED.bit.DBRED = 0;

EPwm11Regs.DBFED.bit.DBFED = 0;

EPwm11Regs.TZCLR.bit.OST = 1; //enable PWM at first

//--------------------------------------------------------------------------------

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; //Start all the timers synced

EDIS;

}