This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

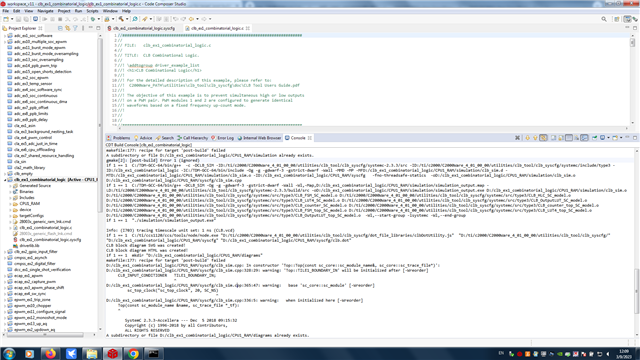

你好, 我们测试CLB 历程,编译的时候报错, 步骤如下。

1:导入TI 提供的 CLB 例子历程 (280039C),可以是任何一个关于CLB 的。

2:编译,出错,我按网上的方法试过也不行,GCC 是推荐的版本。

3: 强行下载下去,功能没反应。CCS 版本11.02

makefile:177: recipe for target 'post-build' failed

D:/clb_ex1_combinatorial_logic/CPU1_RAM/syscfg/clb_sim.cpp: In constructor 'Top::Top(const sc_core::sc_module_name&, sc_core::sc_trace_file*)':

D:/clb_ex1_combinatorial_logic/CPU1_RAM/syscfg/clb_sim.cpp:328:29: warning: 'Top::TILE1_BOUNDARY_IN' will be initialized after [-Wreorder]

CLB_INPUT_CONDITIONER TILE1_BOUNDARY_IN;

^

D:/clb_ex1_combinatorial_logic/CPU1_RAM/syscfg/clb_sim.cpp:365:47: warning: base 'sc_core::sc_module' [-Wreorder]

sc_top_clock("sc_top_clock", 20, SC_NS)

^

D:/clb_ex1_combinatorial_logic/CPU1_RAM/syscfg/clb_sim.cpp:336:5: warning: when initialized here [-Wreorder]

Top(const sc_module_name &name, sc_trace_file *_tf):

^

D:/clb_ex1_combinatorial_logic/CPU1_RAM/syscfg/clb_sim.cpp: 这个路径是怎么来的?不知道是你哪里出了问题。用最新版的C2000Ware试一下。