各位好,最近我在做一版飞跨电容型三电平Buck电路,采用28379D launchpad 在做单电压闭环(飞跨电容电压平衡暂未控制)时出现了在输入达到20V以上后,输出电压开始下降的问题,已知信息如下。

1.采样选用隔离放大器+普通运放调理的电路,用稳定直流电压测试没有问题。

2.采用我的电路板,在开环状态下以不同的占空比输出相同电压(如20V输出8V,30V输出8V),高压输入下用万用表测得采样电路输出电压会更高,在电脑端观察单片机得到的采样数据同样如此。

3.更换功率板到采样板的接线为屏蔽线试图减少干扰后,问题并没有解决。

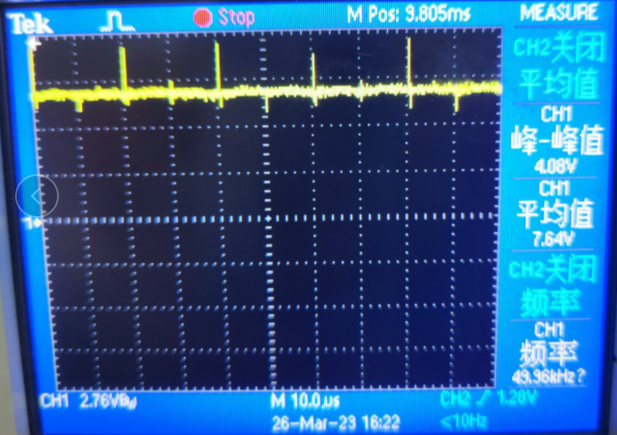

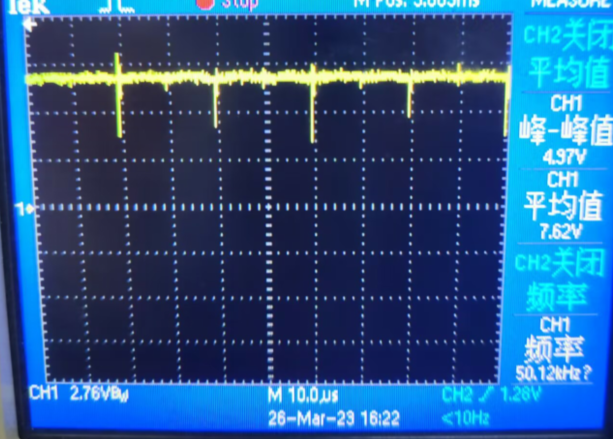

4.约30V输入下输出电压的波形

基于上述两点,我推测是由于高压下输出电压的关断尖峰导致输出电压有效值变高,因此单片机采样值变高,控制开关管占空比下降。接下来做出了如下改变:

开关频率为50kHz。采样频率=开关频率,将采样点修改为开关周期的3/4处试图避开尖峰后,问题并没有解决。(这让我怀疑是否真是因为尖峰导致采样偏高?)

代码如下

void ConfigureADC(void)

{

EALLOW;

AdcaRegs.ADCCTL2.bit.PRESCALE = 0; //ADC时钟分频

AdcSetMode(ADC_ADCA, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);//设定ADC运行模式:12位单输入信号

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1;//转换结束后产生中断脉冲

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1;//开启所有模拟电路

DELAY_US(1000);

AdcbRegs.ADCCTL2.bit.PRESCALE = 0; //ADC时钟分频

AdcSetMode(ADC_ADCB, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);//设定ADC运行模式:12位单输入信号

AdcbRegs.ADCCTL1.bit.INTPULSEPOS = 1;//转换结束后产生中断脉冲

AdcbRegs.ADCCTL1.bit.ADCPWDNZ = 1;//开启所有模拟电路

DELAY_US(1000);

AdccRegs.ADCCTL2.bit.PRESCALE = 0; //ADC时钟分频

AdcSetMode(ADC_ADCC, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);//设定ADC运行模式:12位单输入信号

AdccRegs.ADCCTL1.bit.INTPULSEPOS = 1;//转换结束后产生中断脉冲

AdccRegs.ADCCTL1.bit.ADCPWDNZ = 1;//开启所有模拟电路

DELAY_US(1000);

EDIS;

}

void ConfigureEPWM(void)

{

EALLOW;

// Assumes ePWM clock is already enabled

EPwm1Regs.ETSEL.bit.SOCAEN = 0; // 禁用EWPWMxSOCA脉冲

EPwm1Regs.ETSEL.bit.SOCASEL = 4; // 上升计数

EPwm1Regs.ETPS.bit.SOCAPRD = 1; // 发生事件1时产生脉冲

//下面在单采样时需要设置,本程序中在PWM配置函数中被再次配置

EPwm1Regs.CMPA.bit.CMPA = 750; // Set compare A value to 2048 counts

EPwm1Regs.TBPRD = 999; // Set period to 4096 counts

EPwm1Regs.TBCTL.bit.CTRMODE = 3; // freeze counter

EDIS;

}

void SetupADCEpwm(void)

{

Uint16 acqps = 25;

EALLOW;

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 0; //SOC0转换A0

AdcaRegs.ADCSOC0CTL.bit.ACQPS = acqps; //设定采样窗口时间

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 5; //触发信号 - ePWM1, ADCSOCA

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 0; //EOC0 is trigger for ADCINT1

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; //使能中断标志位

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //make sure INT1 flag is cleared

AdcbRegs.ADCSOC0CTL.bit.CHSEL = 2; //SOC0转换B2

AdcbRegs.ADCSOC0CTL.bit.ACQPS = acqps; //设定采样窗口时间

AdcbRegs.ADCSOC0CTL.bit.TRIGSEL = 5; //触发信号 - ePWM1, ADCSOCA

AdcbRegs.ADCINTSEL1N2.bit.INT1SEL = 0; //EOC0 is trigger for ADCINT1

AdcbRegs.ADCINTSEL1N2.bit.INT1E = 1; //使能中断标志位

AdcbRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //make sure INT1 flag is cleared

AdccRegs.ADCSOC0CTL.bit.CHSEL = 2; //SOC0转换C2

AdccRegs.ADCSOC0CTL.bit.ACQPS = acqps; //设定采样窗口时间

AdccRegs.ADCSOC0CTL.bit.TRIGSEL = 5; //触发信号 - ePWM1, ADCSOCA

AdccRegs.ADCINTSEL1N2.bit.INT1SEL = 0; //EOC0 is trigger for ADCINT1

AdccRegs.ADCINTSEL1N2.bit.INT1E = 1; //使能中断标志位

AdccRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; //make sure INT1 flag is cleared

EDIS;

}

我想尝试通过增加RC snubber减小关断尖峰看看问题能否改善,但MOS封装和电路板布局并不允许。

请问各位有什么建议么?

感谢您的关注,期待您的回答!