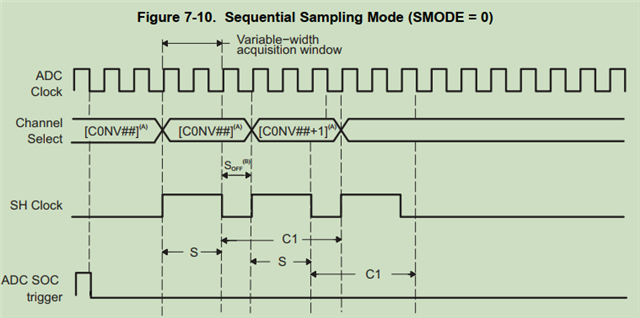

下图为 Technical Reference Manual 中ADC章节中的时序图。因为在我的应用中,对采样时机要求非常细,因此请教以下几个问题:

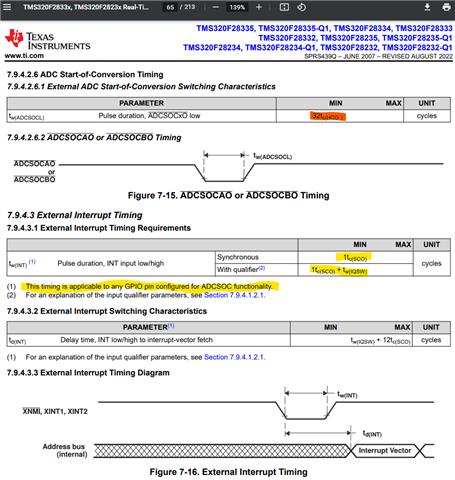

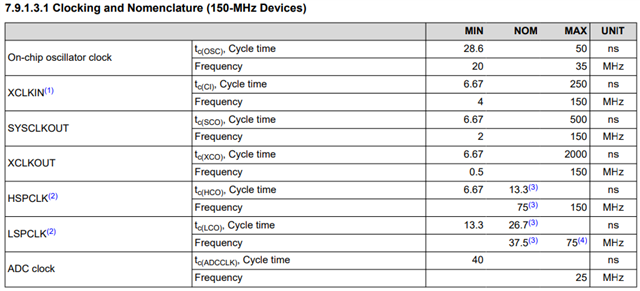

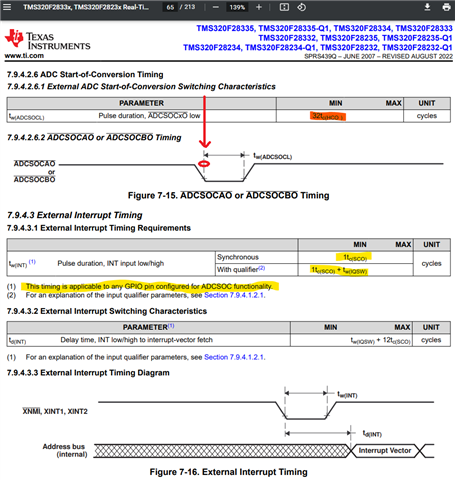

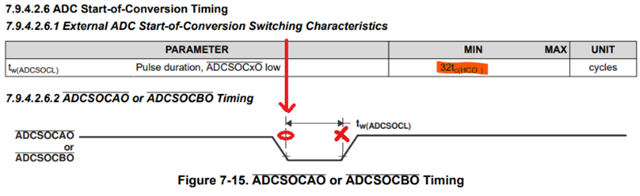

1)设置ADC SOC trigger为EPWM1SOCA。EPWM模块时钟为150MHZ,而ADC模块时钟为25MHZ,那么ADC SOC trigger脉冲宽度是怎样的

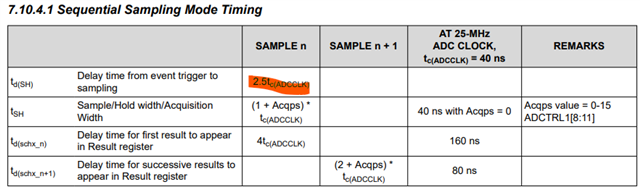

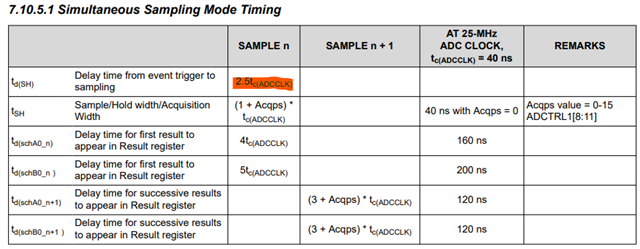

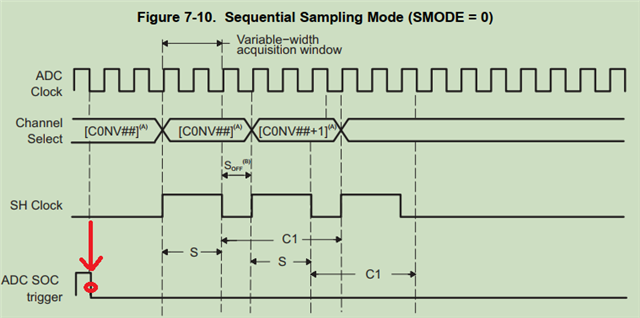

2)从EPWM模块发出SOC信号,到SH Clock信号拉高,开始采样,严格来说是多少时间?从图中看是两个半ADC CLOCK,不是一个整数

3)ADC Clock最大是25MHz吗,在“7.1 Features and Implementation”中提到最大是25MHz,但在“ 7.2.2.1.2 ACQPS Approximation Example for High Bandwidth Signals

”章节的案例中,ADC Clock是30MHz,为什么