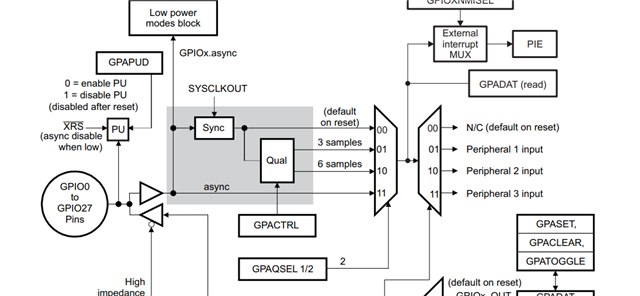

在配置GPIO过程中,将GPIO0,1均配置为输入,且采样周期为系统时钟,采样次数与系统时钟同步。然后用GPADAT寄存器读取,程序如下:

if (GpioDataRegs.GPADAT.bit.GPIO0==0)

{a=a+1;}

if (GpioDataRegs.GPADAT.bit.GPIO1==0)

{b=b+1;}

用ccs的clock功能发现程序从if (GpioDataRegs.GPADAT.bit.GPIO0==0)到if (GpioDataRegs.GPADAT.bit.GPIO1==0)大概10ns

然后将采样周期改为510个系统时钟,采样次数为6个采样周期,执行上述程序,同样发现程序从if (GpioDataRegs.GPADAT.bit.GPIO0==0)到if (GpioDataRegs.GPADAT.bit.GPIO1==0)大概10ns。

即配置输入限定不影响GPADAT读取时间?按照我的理解,GPADAT读取是对GPIO管脚进行采样,检测该管脚电平高低,采样周期越长,读取的时间也应该越长,不知道是否理解有误?