Other Parts Discussed in Thread: LAUNCHXL-F280025C, C2000WARE

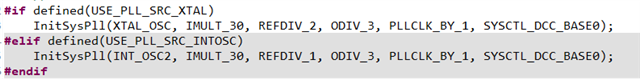

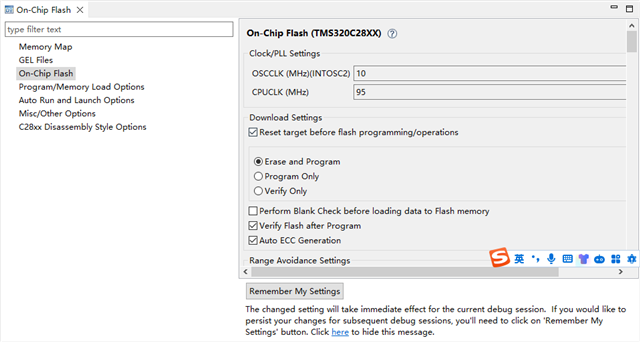

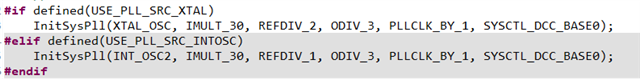

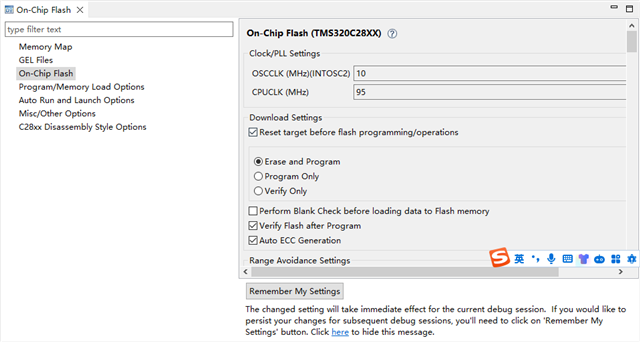

SYSCLK配置的是100MHz,在On-Chip界面显示CPUCLK为95MHz

二者频率为什么不一样?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

SYSCLK配置的是100MHz,在On-Chip界面显示CPUCLK为95MHz

二者频率为什么不一样?

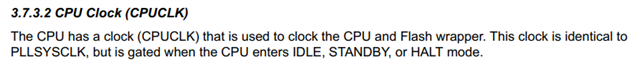

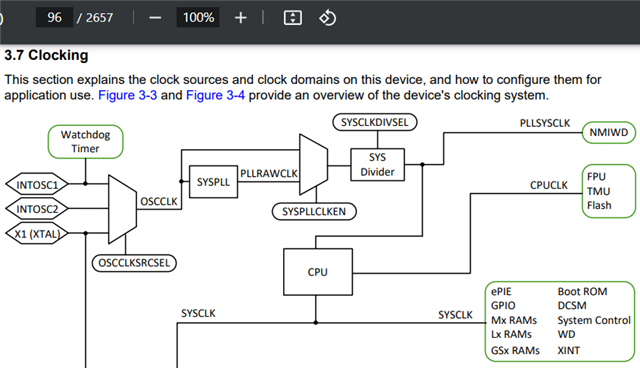

它们之间的关系可以看一下spruin7b_TMS320F28002x Real-Time Microcontrollers Technical Reference Manual (Rev. B)第96页3.7 Clocking:

Since the frequency tolerance of the Internal oscillator is 10MHz +/-2% over full operating range and max device clock frequency is 100MHz, we have some risk of exceeding 100MHz if we choose 10x PLL multiplier with this clock source. Because of this we step back to give 95MHz nominal, and with variation of internal oscillator we will still not violate the 100MHz max.

CCS flash tool always uses internal oscillator since it is known frequency and eliminates need or risk of customer manually entering the value of their external clock(if they have one).

For external X-tal, with tighter tolerance, this is not a concern so we can set PLL to full 100MHz when that is the clock source.