This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

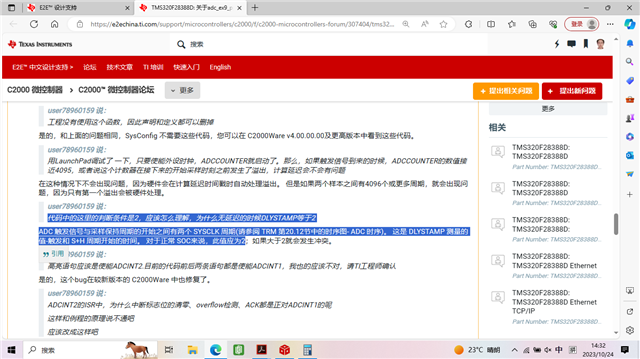

@Cherry Zhou

按照您在

TMS320F28388D: 关于adc_ex9_ppb_delay例程的问题 - C2000︎ 微控制器论坛 - C2000 微控制器 - E2E

设计支持 (ti.com)

中的解答,

“ADC触发信号与采样保持周期的开始之间有2个SYSCLK 周期”

问题1. 鉴于以上考虑,我想cla_ex5_adc_just_in_time例程中GPIO0和GPIO2之间的延迟是不是应该为46个系统时钟而不是44个系统时钟;

问题2. 请问TB-Couter为0与GPIO0跳变为高电平(GPIO0上升沿)之间会有延迟吗?如果也存在2个系统时钟的延迟,那么GPIO0和GPIO2之间延迟应该就还是44个系统时钟

例程中PWM当TB Counter为0时的配置如下

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

您好,

根据原帖中的描述,如果在发出 ePWM SOCA 触发信号时 GPIO0应该变为高电平,那么总数实际上应该为56个周期。 配置为10的采集窗口大小也会计入延迟。 工程师需要一些时间来查看该例程的此问题。同时也希望以上回答会对您有所帮助。