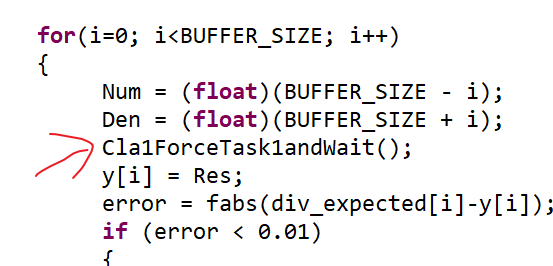

如题,我将官方的配置文件全部复制过来我的工程,但是却无法启动cla,具体现象为:运行到Cla1ForceTask1andWait();时就一直不执行,配置代码为:

//###########################################################################

// FILE: cla_divide_cpu01.c

// TITLE: CLA Divide Example for F2837xS.

//

//! \addtogroup cpu01_example_list

//! <h1>CLA Division: Newton Raphson Approximation (cla_divide_cpu01)</h1>

//!

//! In this example, Task 1 of the CLA will divide two input numbers using

//! multiple approximations in the Newton Raphson method.

//!

//! \b Memory \b Allocation \n

//! - CLA1 to CPU Message RAM

//! - Res - Result of the division operation

//! - CPU to CLA1 Message RAM

//! - Num - Numerator of input

//! - Den - Denominator of input

//!

//! \b Watch \b Variables \n

//! - Num - Numerator of input

//! - Den - Denominator of input

//! - Res - Result of the division operation

//

//###########################################################################

// $TI Release: F2837xS Support Library v190 $

// $Release Date: Mon Feb 1 16:59:09 CST 2016 $

// $Copyright: Copyright (C) 2014-2016 Texas Instruments Incorporated -

// http://www.ti.com/ ALL RIGHTS RESERVED $

//###########################################################################

#include "F28x_Project.h" // Device Headerfile and Examples Include File

#include "cla_divide_shared.h"

//*****************************************************************************

// defines

//*****************************************************************************

//CLA defines

#define WAITSTEP asm(" RPT #255 || NOP")

//*****************************************************************************

// globals

//*****************************************************************************

//Task 1 (C) Variables

// NOTE: Do not initialize the Message RAM variables globally, they will be reset

// during the message ram initialization phase in the CLA memory configuration routine

#ifdef __cplusplus

#pragma DATA_SECTION("CpuToCla1MsgRAM");

float Num;

#pragma DATA_SECTION("CpuToCla1MsgRAM");

float Den;

#pragma DATA_SECTION("Cla1ToCpuMsgRAM");

float Res;

#else

#pragma DATA_SECTION(Num,"CpuToCla1MsgRAM");

float Num;

#pragma DATA_SECTION(Den,"CpuToCla1MsgRAM");

float Den;

#pragma DATA_SECTION(Res,"Cla1ToCpuMsgRAM");

float Res;

#endif //__cplusplus

float y[BUFFER_SIZE];

//Task 2 (C) Variables

//Task 3 (C) Variables

//Task 4 (C) Variables

//Task 5 (C) Variables

//Task 6 (C) Variables

//Task 7 (C) Variables

//Task 8 (C) Variables

//Common (C) Variables

//Golden Test Values

float div_expected[BUFFER_SIZE]={

1, 0.9692308, 0.9393939, 0.9104478, 0.8823529,

0.8550724, 0.8285714, 0.8028169, 0.7777778, 0.7534246,

0.7297297, 0.7066666, 0.6842105, 0.6623377, 0.6410257,

0.6202531, 0.6000000, 0.5802469, 0.5609756, 0.5421687,

0.5238096, 0.5058824, 0.4883721, 0.4712644, 0.4545455,

0.4382023, 0.4222222, 0.4065934, 0.3913043, 0.3763441,

0.3617021, 0.3473684, 0.3333333, 0.3195876, 0.3061225,

0.2929293, 0.2800000, 0.2673267, 0.2549020, 0.2427184,

0.2307692, 0.2190476, 0.2075472, 0.1962617, 0.1851852,

0.1743119, 0.1636364, 0.1531532, 0.1428571, 0.1327434,

0.1228070, 0.1130435, 0.1034483, 0.09401710, 0.08474576,

0.07563026, 0.06666667, 0.05785124, 0.04918033, 0.04065040,

0.03225806, 0.02400000, 0.01587302, 0.007874016

};

uint16_t pass=0;

uint16_t fail=0;

//*****************************************************************************

// function prototypes

//*****************************************************************************

void CLA_runTest(void);

void CLA_configClaMemory(void);

void CLA_initCpu1Cla1(void);

__interrupt void cla1Isr1();

__interrupt void cla1Isr2();

__interrupt void cla1Isr3();

__interrupt void cla1Isr4();

__interrupt void cla1Isr5();

__interrupt void cla1Isr6();

__interrupt void cla1Isr7();

__interrupt void cla1Isr8();

//*****************************************************************************

// Start of main

//*****************************************************************************

void main(void)

{

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the F2837xS_SysCtrl.c file.

InitSysCtrl();

// Step 2. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the F2837xS_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in F2837xS_DefaultIsr.c.

// This function is found in F2837xS_PieVect.c.

InitPieVectTable();

// Step 3. Configure the CLA memory spaces first followed by

// the CLA task vectors

CLA_configClaMemory();

CLA_initCpu1Cla1();

// Step 4. Enable global Interrupts and higher priority real-time debug events:

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

// Step 5. Run the test

CLA_runTest();

}

//*****************************************************************************

// function definitions

//*****************************************************************************

void CLA_runTest(void)

{

int i, error;

for(i=0;i<BUFFER_SIZE;i++)

{

Num = (float)(BUFFER_SIZE - i);

Den = (float)(BUFFER_SIZE + i);

Cla1ForceTask1andWait();

y[i] = Res;

error = fabs(div_expected[i]-y[i]);

if (error < 0.01)

{

pass++;

}

else

{

fail++;

}

}

#if 0

Cla1ForceTask2andWait();

WAITSTEP;

Cla1ForceTask3andWait();

WAITSTEP;

Cla1ForceTask4andWait();

WAITSTEP;

Cla1ForceTask5andWait();

WAITSTEP;

Cla1ForceTask6andWait();

WAITSTEP;

Cla1ForceTask7andWait();

WAITSTEP;

Cla1ForceTask8andWait();

WAITSTEP;

#endif

}

void CLA_configClaMemory(void)

{

extern uint32_t Cla1funcsRunStart, Cla1funcsLoadStart, Cla1funcsLoadSize;

EALLOW;

#ifdef _FLASH

// Copy over code from FLASH to RAM

memcpy((uint32_t *)&Cla1funcsRunStart, (uint32_t *)&Cla1funcsLoadStart,

(uint32_t)&Cla1funcsLoadSize);

#endif //_FLASH

// Initialize and wait for CLA1ToCPUMsgRAM

MemCfgRegs.MSGxINIT.bit.INIT_CLA1TOCPU = 1;

while(MemCfgRegs.MSGxINITDONE.bit.INITDONE_CLA1TOCPU != 1){};

// Initialize and wait for CPUToCLA1MsgRAM

MemCfgRegs.MSGxINIT.bit.INIT_CPUTOCLA1 = 1;

while(MemCfgRegs.MSGxINITDONE.bit.INITDONE_CPUTOCLA1 != 1){};

// Select LS5RAM to be the programming space for the CLA

// First configure the CLA to be the master for LS5 and then

// set the space to be a program block

MemCfgRegs.LSxMSEL.bit.MSEL_LS5 = 1;

MemCfgRegs.LSxCLAPGM.bit.CLAPGM_LS5 = 1;

//Next configure LS0RAM and LS1RAM as data spaces for the CLA

// First configure the CLA to be the master for LS0(1) and then

// set the spaces to be code blocks

MemCfgRegs.LSxMSEL.bit.MSEL_LS0 = 1;

MemCfgRegs.LSxCLAPGM.bit.CLAPGM_LS0 = 0;

MemCfgRegs.LSxMSEL.bit.MSEL_LS1 = 1;

MemCfgRegs.LSxCLAPGM.bit.CLAPGM_LS1 = 0;

EDIS;

}

void CLA_initCpu1Cla1(void)

{

// Compute all CLA task vectors

// On Type-1 CLAs the MVECT registers accept full 16-bit task addresses as

// opposed to offsets used on older Type-0 CLAs

EALLOW;

Cla1Regs.MVECT1 = (uint16_t)(&Cla1Task1);

Cla1Regs.MVECT2 = (uint16_t)(&Cla1Task2);

Cla1Regs.MVECT3 = (uint16_t)(&Cla1Task3);

Cla1Regs.MVECT4 = (uint16_t)(&Cla1Task4);

Cla1Regs.MVECT5 = (uint16_t)(&Cla1Task5);

Cla1Regs.MVECT6 = (uint16_t)(&Cla1Task6);

Cla1Regs.MVECT7 = (uint16_t)(&Cla1Task7);

Cla1Regs.MVECT8 = (uint16_t)(&Cla1Task8);

// Enable the IACK instruction to start a task on CLA in software

// for all 8 CLA tasks. Also, globally enable all 8 tasks (or a

// subset of tasks) by writing to their respective bits in the

// MIER register

Cla1Regs.MCTL.bit.IACKE = 1;

Cla1Regs.MIER.all = 0x00FF;

// Configure the vectors for the end-of-task interrupt for all

// 8 tasks

PieVectTable.CLA1_1_INT = &cla1Isr1;

PieVectTable.CLA1_2_INT = &cla1Isr2;

PieVectTable.CLA1_3_INT = &cla1Isr3;

PieVectTable.CLA1_4_INT = &cla1Isr4;

PieVectTable.CLA1_5_INT = &cla1Isr5;

PieVectTable.CLA1_6_INT = &cla1Isr6;

PieVectTable.CLA1_7_INT = &cla1Isr7;

PieVectTable.CLA1_8_INT = &cla1Isr8;

// Enable CLA interrupts at the group and subgroup levels

PieCtrlRegs.PIEIER11.all = 0xFFFF;

IER |= (M_INT11 );

}

//*****************************************************************************

// ISR

//*****************************************************************************

__interrupt void cla1Isr1 ()

{

// Acknowledge the end-of-task interrupt for task 1

PieCtrlRegs.PIEACK.all = M_INT11;

// asm(" ESTOP0");

}

__interrupt void cla1Isr2 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr3 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr4 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr5 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr6 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr7 ()

{

asm(" ESTOP0");

}

__interrupt void cla1Isr8 ()

{

// Acknowledge the end-of-task interrupt for task 8

PieCtrlRegs.PIEACK.all = M_INT11;

// asm(" ESTOP0");

}

// End of File

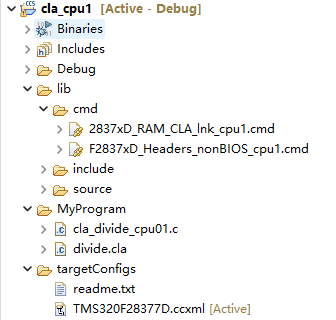

整体工程如下:

文件目录如下:

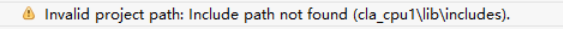

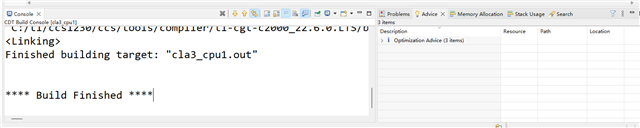

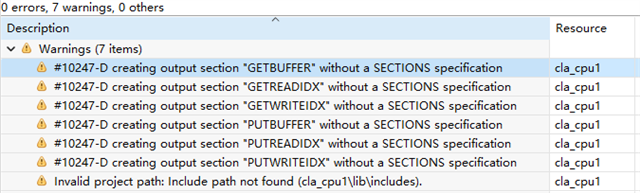

编译的时候还出现了以下的警告:

请问到底是哪里出了问题呢?