Part Number: TMS320F280049C

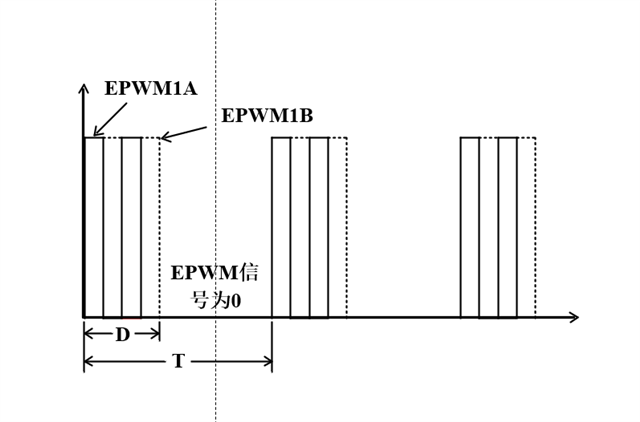

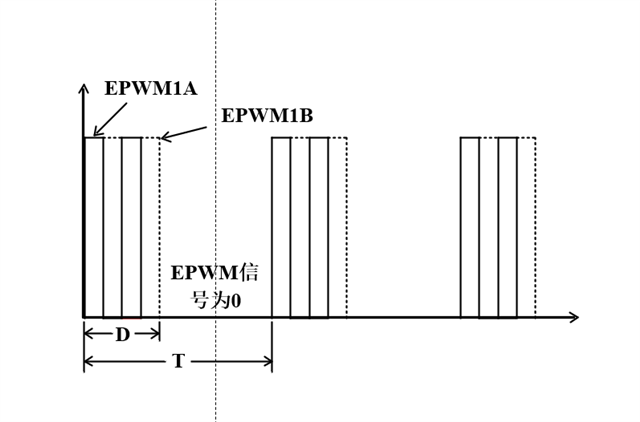

图一 图二 图三

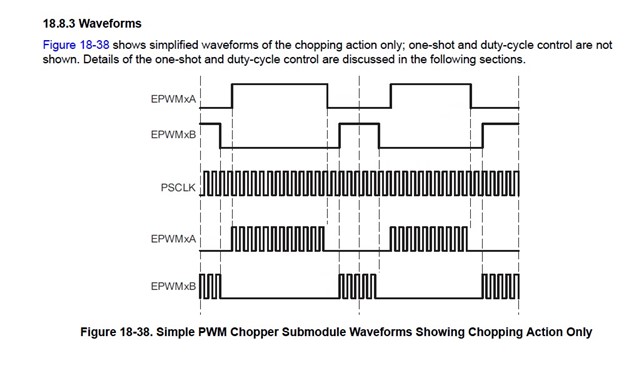

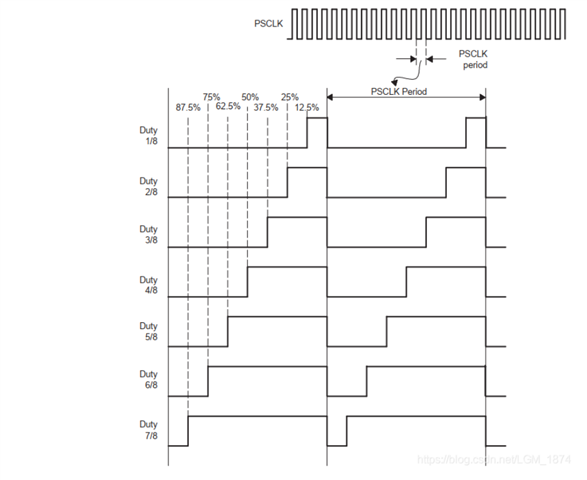

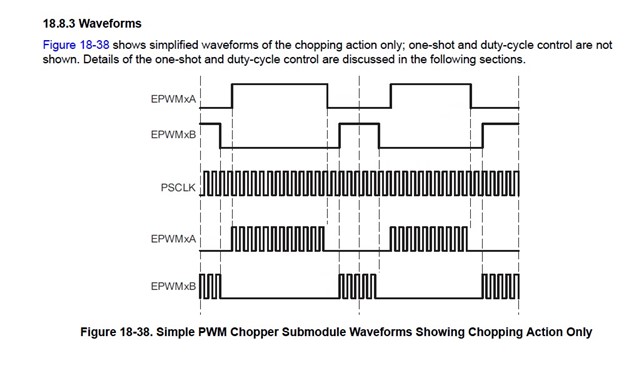

我想实现图一这样的EPWM互补信号,循环周期为T,占空比是指epwm互补信号占周期T的多少,然后我想通过PC模块去实现,但是我找不到PSCLK时钟设置的地方,PSCLK的周期是否可以设置的比epwm1的周期大,如果可以比epwm的周期大,然后通过PC 模块通过对 CHPDUTY 位编程,就可以实现我的需求了。或者请问一下,还有什么方法可以实现我的需求

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320F280049C

图一 图二 图三

我想实现图一这样的EPWM互补信号,循环周期为T,占空比是指epwm互补信号占周期T的多少,然后我想通过PC模块去实现,但是我找不到PSCLK时钟设置的地方,PSCLK的周期是否可以设置的比epwm1的周期大,如果可以比epwm的周期大,然后通过PC 模块通过对 CHPDUTY 位编程,就可以实现我的需求了。或者请问一下,还有什么方法可以实现我的需求

但是我找不到PSCLK时钟设置的地方,

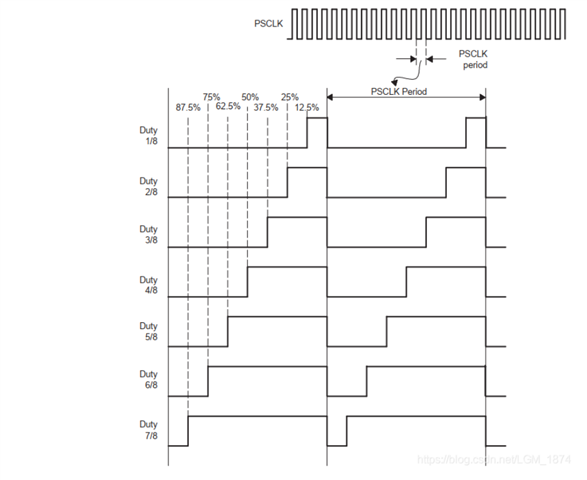

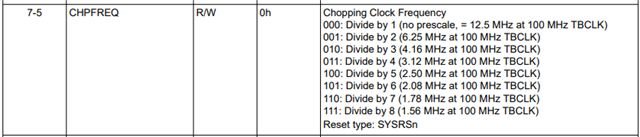

请看一下TRM第2036页18.17.2.11 PCCTL Register (Offset = 14h) [Reset = 0000h]:

https://www.ti.com.cn/cn/lit/ug/sprui33g/sprui33g.pdf

这个位域控制PSCLK;

PSCLK的周期是否可以设置的比epwm1的周期大,

这个具体要看周期值是多少,以及时钟的配置;

然后通过PC 模块通过对 CHPDUTY 位编程,

这个占空比是指每个斩波的百分比。

我在simulink中,通过计数器来记录pwm脉冲数来实现循环周期T,然后通过另一组pwm信号进行与逻辑可以实现占空比D,但我初学ccs,在这里实现不了

这些可以用CLB来实现。CLB其实可以看做一块集成到C2000器件内部的FPGA/CPLD,但是信号链的路径大大缩短,并且结合syscfg图形化工具,不需要去学习verilog语言、在了解模块功能后即可直接配置。

CLB中的计数器可以实现计数功能,查找表可以实现逻辑运算功能。

可以通过CLB Academy来入门:Configurable Logic Block (CLB)

更多内容可以查看TRM中的相关章节:TMS320F28004x Real-Time Microcontrollers Technical Reference Manual第2821页Chapter 29 Configurable Logic Block (CLB)