Part Number: TMS320F28388D

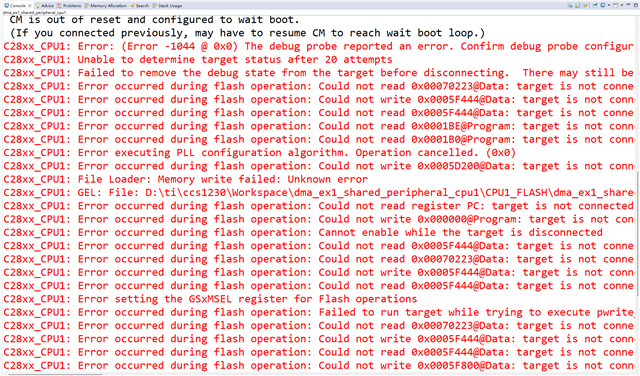

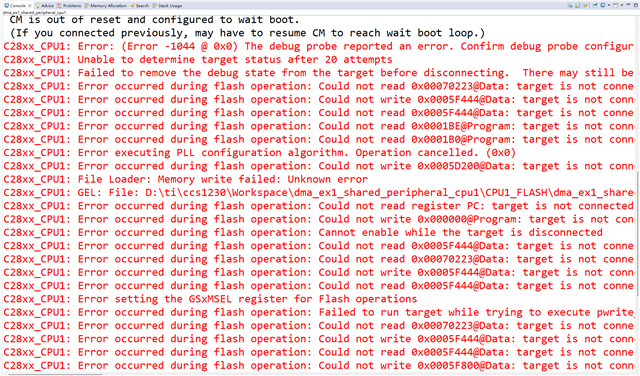

自制电路,28388D的bootmode选择为SCI/Wait,使用dma_ex1_shared_peripheral_cpu1和dma_ex1_shared_peripheral_cpu2的例程。CPU2的例程能够正常烧写进RAM或FLASH并且运行,但是CPU1的例程只能烧写RAM运行,烧写FLASH时,LOAD的时候会出现一堆错误报告。

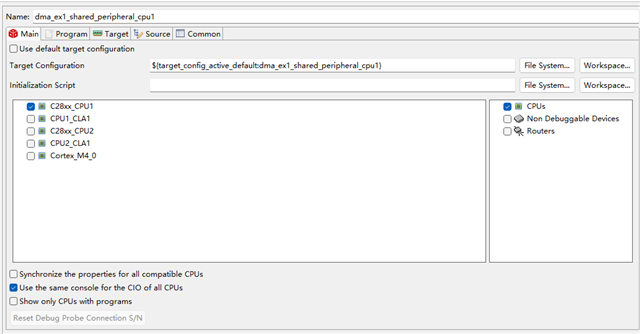

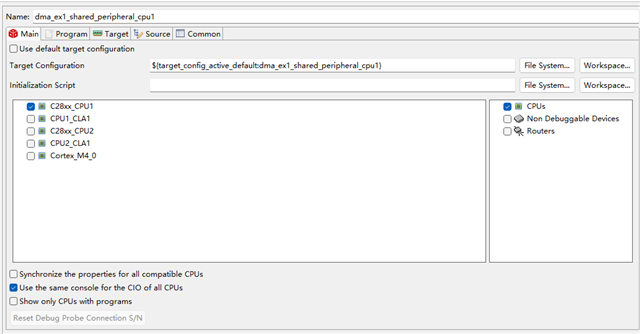

烧写设置只选择了CPU1

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320F28388D

自制电路,28388D的bootmode选择为SCI/Wait,使用dma_ex1_shared_peripheral_cpu1和dma_ex1_shared_peripheral_cpu2的例程。CPU2的例程能够正常烧写进RAM或FLASH并且运行,但是CPU1的例程只能烧写RAM运行,烧写FLASH时,LOAD的时候会出现一堆错误报告。

烧写设置只选择了CPU1

你好,非常感谢您的回应。

我们使用了两个电路板,多个XDS100V3仿真器,结果是一样的。

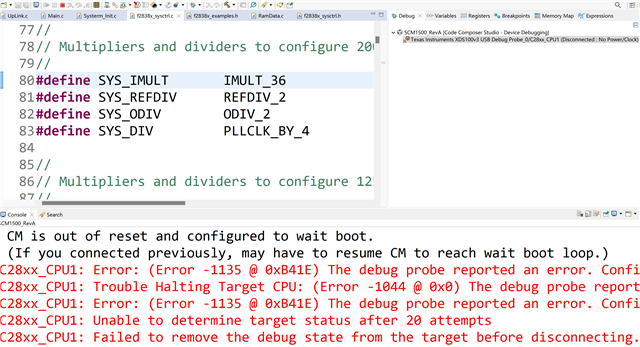

有一点很奇怪,在使用CPU1的RAM调试时,需要通过设置,将InitSysPll()中通过SYS_IMULT、SYS_REFDIV、SYS_ODIV和SYS_DIV设置的系统时钟降低到一定值时,RAM才能够调试运行。例如SYS_IMULT = IMULT_36、SYS_REFDIV = REFDIV_2、SYS_ODIV = ODIV_2和SYS_DIV = PLLCLK_BY_4时,RAM运行会显示和烧写FLASH前三条一样的错误,如图。当降低到SYS_IMULT = IMULT_32时,RAM调试可以正常运行。

想问一下,是否XDS100V3不太适用于F28388D

谢谢