在调整相位的过程中有点问题,

EPwm1Regs.CMPA.half.CMPA = 835;

EPwm1Regs.CMPB = 745;

EPwm1Regs.TBPRD = 1580;

EPwm2Regs.CMPA.half.CMPA = 835;

EPwm2Regs.CMPB = 745;

EPwm2Regs.TBPRD = 1580;

EPwm2Regs.TBPHS.half.TBPHS = 0;

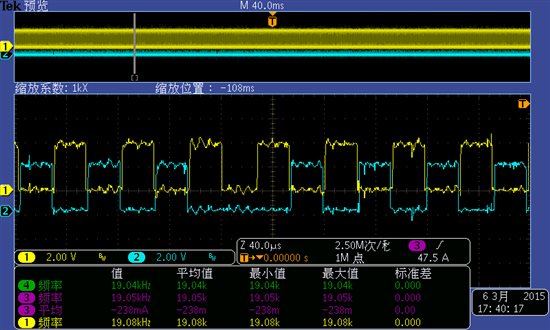

现象是:

1.逐步增加相位差(即EPwm2Regs.TBPHS.half.TBPHS逐渐增大,每次加1,最大不超过周期EPwm1Regs.TBPRD = 1580),一切正常。

2.但是,再向下减相位时(即EPwm2Regs.TBPHS.half.TBPHS逐渐减少,每次减1,减到0为止),在两个点有问题,EPwm2Regs.TBPHS.half.TBPHS = 835时(刚好是CMPA 的值),再向下减1(即EPwm2Regs.TBPHS.half.TBPHS = 834,有嗒的一声),在EPwm2Regs.TBPHS.half.TBPHS = 745时(刚好是CMPB 值),再向下减1(即EPwm2Regs.TBPHS.half.TBPHS = 744,有嗒的一声),请问这是什么原因,应该不是巧合,是不是那个地方配置还有问题,求解?

初始化代码如下:

void InitEPwm1(void)

{

// Enable TZ1 and TZ2 as one shot trip sources

EALLOW;

EPwm1Regs.TZSEL.bit.OSHT1 = 1;

EPwm1Regs.TZSEL.bit.OSHT2 = 1;

// What do we want the TZ1 and TZ2 to do?

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_HI;

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_HI;

// Enable TZ interrupt

//EPwm1Regs.TZEINT.bit.OST = 1;

EDIS;

// Setup TBCLK

EPwm1Regs.TBPRD =EPWM1_TIMER_TBPRD; //600; // Set timer period 801 TBCLKs

EPwm1Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

//EPwm1Regs.TBCTL.bit.PRDLD = 0;

// Set Compare values

EPwm1Regs.CMPA.half.CMPA = EPWM1_MIN_CMPA;//324;//; // Set compare A value

EPwm1Regs.CMPB = EPWM1_MIN_CMPB;//276;//; // Set Compare B value

// Setup counter mode

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

//EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;//0x0-1分频,TBCLK = SYSCLKOUT / (HSPCLKDIV × CLKDIV)

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // Sync down-stream module

// Setup shadowing

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

#if 1

// Action Qualifier SubModule Registers

//EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;//AQ_CLEAR;

//EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;//AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET;//AQ_SET;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

#endif

#if 1

// Interrupt where we will change the Compare Values

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTRU_CMPB;//ET_CTR_ZERO; // Select INT on Zero event

mPWM1_Disable(); // Disable INT ,close pwm disable,open pwm enable

EPwm1Regs.ETPS.bit.INTPRD = ET_2ND; // Generate INT on 3rd event

#endif

#if 1

EALLOW;

//===========================================================================

// TZA events can force EPWMxA

// TZB events can force EPWMxB

#if 1

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_HI; // EPWM1A will go low //故障产生时的保护

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_HI; // EPWM1B will go low

#endif

EPwm1Regs.TZFRC.bit.OST = 1; // Turn off the PWM

EDIS;

#endif

}

void InitEPwm2(void)

{

#if 1

// Enable TZ1 and TZ2 as one shot trip sources

EALLOW;

EPwm2Regs.TZSEL.bit.OSHT1 = 1;

EPwm2Regs.TZSEL.bit.OSHT2 = 1;

// What do we want the TZ1 and TZ2 to do?

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_HI;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_HI;

// Enable TZ interrupt

//EPwm2Regs.TZEINT.bit.OST = 1;

EDIS;

#endif

// Setup TBCLK

EPwm2Regs.TBPRD =EPWM2_TIMER_TBPRD; //600; // Set timer period 801 TBCLKs

EPwm2Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

//EPwm2Regs.TBCTL.bit.PRDLD = 0;

// Set Compare values

EPwm2Regs.CMPA.half.CMPA = EPWM2_MIN_CMPA;//324;//; // Set compare A value

EPwm2Regs.CMPB = EPWM2_MIN_CMPB;//276;//; // Set Compare B value

// Setup counter mode

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

//EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;//0x0-1分频,TBCLK = SYSCLKOUT / (HSPCLKDIV × CLKDIV)

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Slave module

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through

// Setup shadowing

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

#if 1

// Action Qualifier SubModule Registers

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;//AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CAD = AQ_SET;//AQ_SET;

EPwm2Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm2Regs.AQCTLB.bit.CBD = AQ_CLEAR;

#endif

#if 1

// Interrupt where we will change the Compare Values

EPwm2Regs.ETSEL.bit.INTSEL = ET_CTRU_CMPB;//ET_CTR_ZERO; // Select INT on Zero event

mPWM2_Disable(); // Disable INT ,close pwm disable,open pwm enable

EPwm2Regs.ETPS.bit.INTPRD = ET_2ND; // Generate INT on 3rd event

#endif

#if 1

EALLOW;

//===========================================================================

// TZA events can force EPWMxA

// TZB events can force EPWMxB

#if 1

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_HI;//硬件反向了 // EPWM1A will go low //故障产生时的保护

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_HI; // EPWM1B will go low

#endif

EPwm2Regs.TZFRC.bit.OST = 1; // Turn off the PWM

EDIS;

#endif

}