ADCSOC使用顺序采样,采样频率为70KHz。

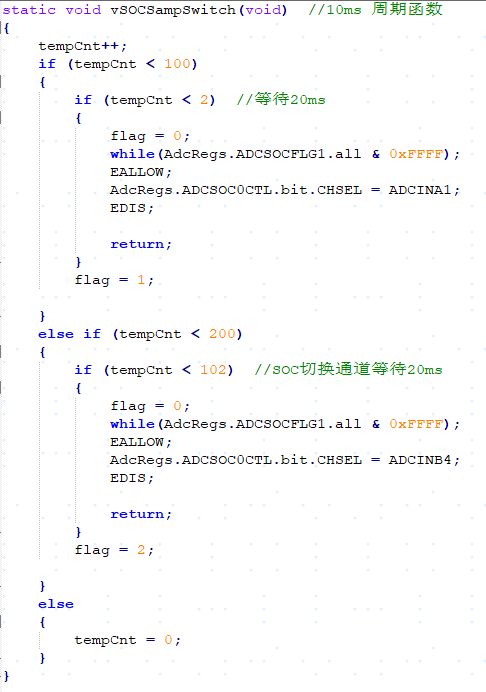

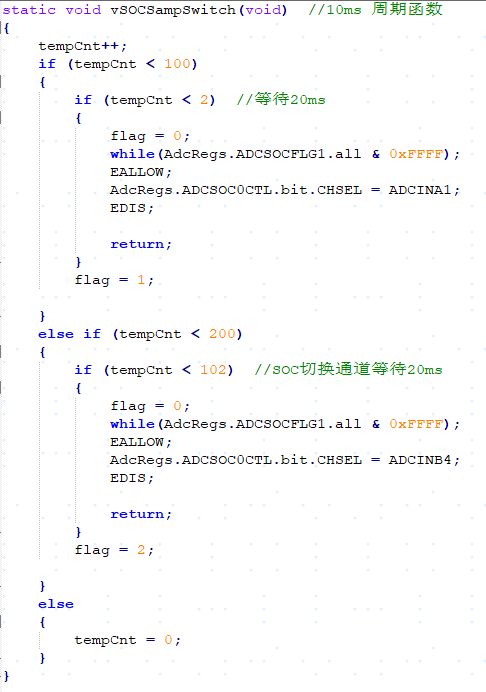

当SOC0通道进行切换的时候,例如SOC0,1s采样ADCINA1,1s采样ADCINB4,这样操作为什么会影响到其他通道的采样?

例如:

但有时候又不会有影响,例如SOC,在ADCINA1和ADCINB7,之间行进切换

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

ADCSOC使用顺序采样,采样频率为70KHz。

当SOC0通道进行切换的时候,例如SOC0,1s采样ADCINA1,1s采样ADCINB4,这样操作为什么会影响到其他通道的采样?

例如:

但有时候又不会有影响,例如SOC,在ADCINA1和ADCINB7,之间行进切换

您好,

SOC的触发源一样的吗?

在TRM中“8.2 SOC Principle of Operation”有SOC使用的应用示例,确定符合您应用的案例。

TMS320F2803x Microcontrollers Technical Reference Manual (Rev. A)

同时请参考示例代码Example_2803xAdcSoc.c

您好,

可能你还没理解我的问题,并不是ADC采样不能正常触发,而是使用pwm周期(70Khz)触发ADC采样,采样数值正常,以上都没有问题,但我想实现的是SOC0,1s采样ADCINA1,1s采样ADCINB4,即一个soc采两个ADC

初始化代码:

void InitAdc(void)

{

// *IMPORTANT*

// The Device_cal function, which copies the ADC calibration values from TI reserved

// OTP into the ADCREFSEL and ADCOFFTRIM registers, occurs automatically in the

// Boot ROM. If the boot ROM code is bypassed during the debug process, the

// following function MUST be called for the ADC to function according

// to specification. The clocks to the ADC MUST be enabled before calling this

// function.

// See the device data manual and/or the ADC Reference

// Manual for more information.

EALLOW;

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1;

(*Device_cal)();

EDIS;

// To powerup the ADC the ADCENCLK bit should be set first to enable

// clocks, followed by powering up the bandgap, reference circuitry, and ADC core.

// Before the first conversion is performed a 5ms delay must be observed

// after power up to give all analog circuits time to power up and settle

// Please note that for the delay function below to operate correctly the

// CPU_RATE define statement in the DSP2803x_Examples.h file must

// contain the correct CPU clock period in nanoseconds.

EALLOW;

AdcRegs.ADCCTL1.bit.ADCREFSEL = 1; // Select external BG

AdcRegs.ADCCTL1.bit.ADCBGPWD = 1; // Power ADC BG

AdcRegs.ADCCTL1.bit.ADCREFPWD = 1; // Power reference

AdcRegs.ADCCTL1.bit.ADCPWDN = 1; // Power ADC

AdcRegs.ADCCTL2.bit.ADCNONOVERLAP = 1; // Overlap of sample is not allowed

AdcRegs.ADCCTL2.bit.CLKDIV2EN = 0; // 0 :ADC clock = CPU clock //1: ADC clock = CPU clock/2

AdcRegs.ADCCTL1.bit.ADCENABLE = 1; // Enable ADC

EDIS;

DELAY_US_APP(ADC_usDELAY);

AdcOffsetSelfCal();

EALLOW;

AdcRegs.ADCCTL1.bit.ADCREFSEL = 1; // Select external BG

AdcRegs.ADCSAMPLEMODE.all = 0; // Single sample mode

AdcRegs.ADCSOC0CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC0CTL.bit.CHSEL = ADCASOC0;

AdcRegs.ADCSOC0CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC1CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC1CTL.bit.CHSEL = ADCASOC1;

AdcRegs.ADCSOC1CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC2CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC2CTL.bit.CHSEL = ADCASOC2;

AdcRegs.ADCSOC2CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC3CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC3CTL.bit.CHSEL = ADCASOC3;

AdcRegs.ADCSOC3CTL.bit.ACQPS = 0xA;

AdcRegs.ADCSOC4CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC4CTL.bit.CHSEL = ADCASOC4;

AdcRegs.ADCSOC4CTL.bit.ACQPS = SAMPLE_WINDOW;//0x10;

AdcRegs.ADCSOC5CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC5CTL.bit.CHSEL = ADCASOC5;

AdcRegs.ADCSOC5CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC6CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC6CTL.bit.CHSEL = ADCASOC6;

AdcRegs.ADCSOC6CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC7CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC7CTL.bit.CHSEL = ADCASOC7;

AdcRegs.ADCSOC7CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC8CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC8CTL.bit.CHSEL = ADCASOC8;

AdcRegs.ADCSOC8CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC9CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC9CTL.bit.CHSEL = ADCASOC9;

AdcRegs.ADCSOC9CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC10CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC10CTL.bit.CHSEL = ADCASOC10;

AdcRegs.ADCSOC10CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC11CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC11CTL.bit.CHSEL = ADCASOC11;

AdcRegs.ADCSOC11CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC12CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC12CTL.bit.CHSEL = ADCASOC12;

AdcRegs.ADCSOC12CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC13CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC13CTL.bit.CHSEL = ADCASOC13;

AdcRegs.ADCSOC13CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC14CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC14CTL.bit.CHSEL = ADCASOC14;

AdcRegs.ADCSOC14CTL.bit.ACQPS = SAMPLE_WINDOW;

AdcRegs.ADCSOC15CTL.bit.TRIGSEL = SAMP_TRIG;

AdcRegs.ADCSOC15CTL.bit.CHSEL = ADCASOC15;

AdcRegs.ADCSOC15CTL.bit.ACQPS = TDSP_WINDOW;

AdcRegs.SOCPRICTL.bit.SOCPRIORITY = SAME_PRIORITY;

AdcRegs.ADCCTL1.bit.VREFLOCONV = 1; //Select VREFLO connection on B5

//round cycle ???

// AdcRegs.SOCPRICTL.bit.RRPOINTER = 0x0F;

EDIS;

}