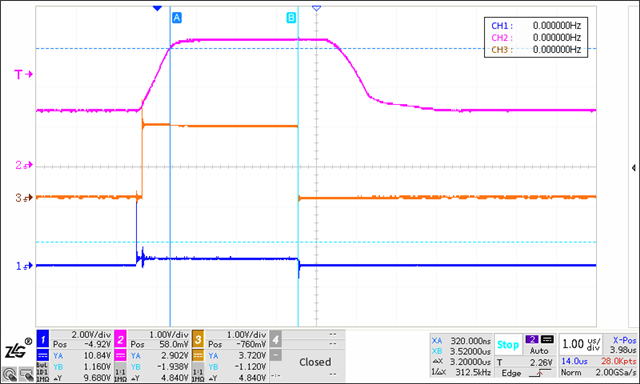

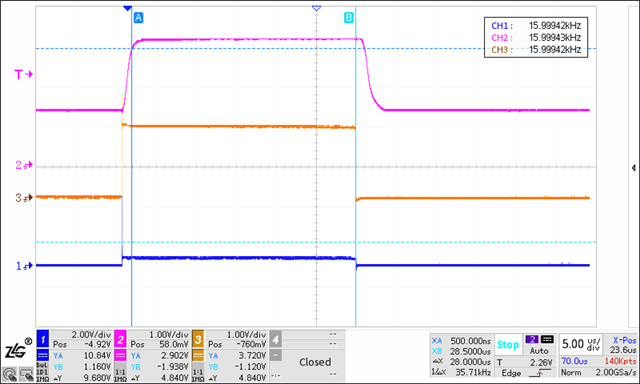

我们使用此universal_motorcontrol_lab_f280015x工程做电机硬件过流响应时间性能测试,发现U相、V相硬件过流响应时间为3.2us,W相硬件过流响应时间为28us,使用2800157芯片,此工程硬件过流配置为,使用芯片内部CMPSS比较器,通过epwmxbar将比较器信号引入epwm模块,通过DC和TZ子模块使PWM输出强制停止,如何配置可以缩短硬件过流响应时间,即从过流电流发生到pwm强制关断的时间缩短为6us以内?

CMPSS比较器配置如下:

// CMPSS - Three phase current

#define MTR1_CMPSS_U_BASE CMPSSLITE3_BASE

#define MTR1_CMPSS_V_BASE CMPSSLITE3_BASE

#define MTR1_CMPSS_W_BASE CMPSS1_BASE

obj->cmpssHandle[0] = MTR1_CMPSS_U_BASE; //!< the CMPSS handle

obj->cmpssHandle[1] = MTR1_CMPSS_V_BASE; //!< the CMPSS handle

obj->cmpssHandle[2] = MTR1_CMPSS_W_BASE; //!< the CMPSS handle

void HAL_setupCMPSSs(HAL_MTR_Handle handle)

{

HAL_MTR_Obj *obj = (HAL_MTR_Obj *)handle;

#if defined(MOTOR1_ISBLDC) || defined(MOTOR1_DCLINKSS)

#else // !(MOTOR1_ISBLDC || MOTOR1_DCLINKSS)

// Refer to Technical Reference Manual to configure the ePWM X-Bar

uint16_t cmpsaDACH = MTR1_CMPSS_DACH_VALUE;

uint16_t cmpsaDACL = MTR1_CMPSS_DACL_VALUE;

#if defined(HVMTRPFC_REV1P1)

ASysCtl_selectCMPHPMux(MTR1_IU_CMPHP_SEL, MTR1_IU_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR1_IU_CMPLP_SEL, MTR1_IU_CMPLP_MUX);

ASysCtl_selectCMPHPMux(MTR1_IV_CMPHP_SEL, MTR1_IV_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR1_IV_CMPLP_SEL, MTR1_IV_CMPLP_MUX);

ASysCtl_selectCMPHPMux(MTR1_IW_CMPHP_SEL, MTR1_IW_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR1_IW_CMPLP_SEL, MTR1_IW_CMPLP_MUX);

//----- U Phase ------------------------------------------------------------

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(obj->cmpssHandle[0]);

// NEG signal from DAC for COMP-H

CMPSS_configHighComparator(obj->cmpssHandle[0], CMPSS_INSRC_DAC);

// NEG signal from DAC for COMP-L

CMPSS_configLowComparator(obj->cmpssHandle[0], CMPSS_INSRC_DAC);

// Configure the output signals. Both CTRIPH and CTRIPOUTH will be fed by

// the asynchronous comparator output.

// Dig filter output ==> CTRIPH, Dig filter output ==> CTRIPOUTH

CMPSS_configOutputsHigh(obj->cmpssHandle[0],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER);

// Dig filter output ==> CTRIPL, Dig filter output ==> CTRIPOUTL

CMPSS_configOutputsLow(obj->cmpssHandle[0],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER |

CMPSS_INV_INVERTED);

// Configure digital filter. For this example, the maxiumum values will be

// used for the clock prescale, sample window size, and threshold.

CMPSS_configFilterHigh(obj->cmpssHandle[0], 32, 32, 10);

CMPSS_initFilterHigh(obj->cmpssHandle[0]);

// Initialize the filter logic and start filtering

CMPSS_configFilterLow(obj->cmpssHandle[0], 32, 32, 10);

CMPSS_initFilterLow(obj->cmpssHandle[0]);

// Set up COMPHYSCTL register

// COMP hysteresis set to 2x typical value

CMPSS_setHysteresis(obj->cmpssHandle[0], 1);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for

// arbitrary reference

CMPSS_configDAC(obj->cmpssHandle[0],

CMPSS_DACVAL_SYSCLK | CMPSS_DACSRC_SHDW);

// Set DAC-H to allowed MAX +ve current

CMPSS_setDACValueHigh(obj->cmpssHandle[0], cmpsaDACH);

// Set DAC-L to allowed MAX -ve current

CMPSS_setDACValueLow(obj->cmpssHandle[0], cmpsaDACL);

// Clear any high comparator digital filter output latch

CMPSS_clearFilterLatchHigh(obj->cmpssHandle[0]);

// Clear any low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[0]);

//---------------- V pHase -------------------------------------------------

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(obj->cmpssHandle[1]);

// NEG signal from DAC for COMP-H

CMPSS_configHighComparator(obj->cmpssHandle[1], CMPSS_INSRC_DAC);

// NEG signal from DAC for COMP-L

CMPSS_configLowComparator(obj->cmpssHandle[1], CMPSS_INSRC_DAC);

// Configure the output signals. Both CTRIPH and CTRIPOUTH will be fed by

// the asynchronous comparator output.

// Dig filter output ==> CTRIPH, Dig filter output ==> CTRIPOUTH

CMPSS_configOutputsHigh(obj->cmpssHandle[1],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER);

// Dig filter output ==> CTRIPL, Dig filter output ==> CTRIPOUTL

CMPSS_configOutputsLow(obj->cmpssHandle[1],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER |

CMPSS_INV_INVERTED);

// Configure digital filter. For this example, the maxiumum values will be

// used for the clock prescale, sample window size, and threshold.

CMPSS_configFilterHigh(obj->cmpssHandle[1], 32, 32, 10);

CMPSS_initFilterHigh(obj->cmpssHandle[1]);

// Initialize the filter logic and start filtering

CMPSS_configFilterLow(obj->cmpssHandle[1], 32, 32, 10);

CMPSS_initFilterLow(obj->cmpssHandle[1]);

// Set up COMPHYSCTL register

// COMP hysteresis set to 2x typical value

CMPSS_setHysteresis(obj->cmpssHandle[1], 1);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for

// arbitrary reference

CMPSS_configDAC(obj->cmpssHandle[1],

CMPSS_DACVAL_SYSCLK | CMPSS_DACSRC_SHDW);

// Set DAC-H to allowed MAX +ve current

CMPSS_setDACValueHigh(obj->cmpssHandle[1], cmpsaDACH);

// Set DAC-L to allowed MAX -ve current

CMPSS_setDACValueLow(obj->cmpssHandle[1], cmpsaDACL);

// Clear any high comparator digital filter output latch

CMPSS_clearFilterLatchHigh(obj->cmpssHandle[1]);

// Clear any low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[1]);

//---------------- W Phase -------------------------------------------------

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(obj->cmpssHandle[2]);

// NEG signal from DAC for COMP-H

CMPSS_configHighComparator(obj->cmpssHandle[2], CMPSS_INSRC_DAC);

// NEG signal from DAC for COMP-L

CMPSS_configLowComparator(obj->cmpssHandle[2], CMPSS_INSRC_DAC);

// Configure the output signals. Both CTRIPH and CTRIPOUTH will be fed by

// the asynchronous comparator output.

// Dig filter output ==> CTRIPH, Dig filter output ==> CTRIPOUTH

CMPSS_configOutputsHigh(obj->cmpssHandle[2],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER);

// Dig filter output ==> CTRIPL, Dig filter output ==> CTRIPOUTL

CMPSS_configOutputsLow(obj->cmpssHandle[2],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER |

CMPSS_INV_INVERTED);

// Configure digital filter. For this example, the maxiumum values will be

// used for the clock prescale, sample window size, and threshold.

CMPSS_configFilterHigh(obj->cmpssHandle[2], 32, 32, 10);

CMPSS_initFilterHigh(obj->cmpssHandle[2]);

// Initialize the filter logic and start filtering

CMPSS_configFilterLow(obj->cmpssHandle[2], 32, 32, 10);

CMPSS_initFilterLow(obj->cmpssHandle[2]);

// Set up COMPHYSCTL register

// COMP hysteresis set to 2x typical value

CMPSS_setHysteresis(obj->cmpssHandle[2], 1);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for

// arbitrary reference

CMPSS_configDAC(obj->cmpssHandle[2],

CMPSS_DACVAL_SYSCLK | CMPSS_DACSRC_SHDW);

// Set DAC-H to allowed MAX +ve current

CMPSS_setDACValueHigh(obj->cmpssHandle[2], cmpsaDACH);

// Set DAC-L to allowed MAX -ve current

CMPSS_setDACValueLow(obj->cmpssHandle[2], cmpsaDACL);

// Clear any high comparator digital filter output latch

CMPSS_clearFilterLatchHigh(obj->cmpssHandle[2]);

// Clear any low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[2]);

// HVMTRPFC_REV1P1

#endif // !HVMTRPFC_REV1P1

#endif // !(MOTOR1_ISBLDC || MOTOR1_DCLINKSS)

return;

} // end of HAL_setupCMPSSs() function