Part Number: TMS320F28335

芯片以28335为例,28035 28069 以及更新的280049也有类似的问题。

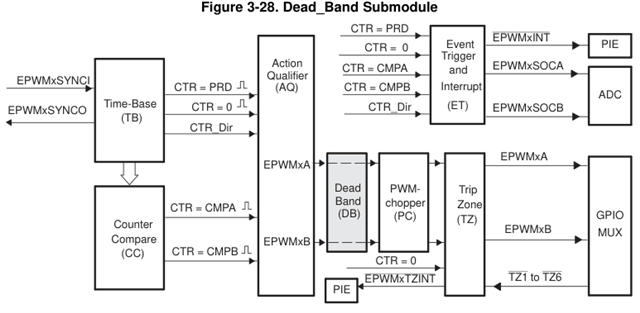

硬件上DB模块位于AQ模块的后面,接受AQ模块的输出,在AQ模块中可以设置各种波形输出,也可以非常方便地封锁脉冲。

DB模块如下,接受两个AQ模块的输出,内部带了两个反相器,常见的互补死区模式,目前用法都是使用一个EPWMxA作为输入,使用DB模块内部的反相器生成一对互补信号作为输出,这样带来一个问题就是无论AQ模块中怎么操作,最终DB模块的输出PWM都是一高一低,半桥模块的下管始终是导通的。无法彻底关断。为了输出两个全低的信号,往往要使用后面的TZ模块来封锁脉冲。然而TZ模块又做不到同步开启脉冲,在开启脉冲的时候首个脉冲占空比都是错误的。

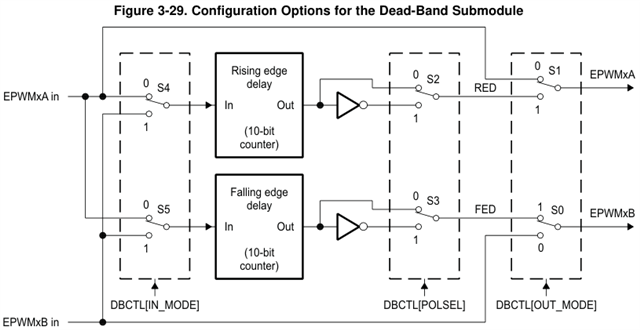

实际上AQ模块输出一对互补无死区的脉冲是非常简单的,在DB模块中只要给对应的边沿增加延迟即可。目前 DB模块是给一个信号上升沿做延迟,一个信号下降沿做延迟,然而很不幸的是。对于AQ输出的互补信号,上升沿和下降沿实际是原始信号的同一个边沿,给同一个边沿加死区就是没有死区。如果DB模块都给上升沿做延迟,那死区就很容易实现,而且实现死区以后,依然可以使用AQ模块来封锁脉冲。

芯片硬件解决方法很简单:DB模块里面两个延迟硬件可以设置对上升沿或者下降沿做延迟就可以了。