用HCG生成的代码,配置如下图所示

我DEBUG时,PIN3的PWM波形正常,

但在void hetLowLevelInterrupt(void)以及void hetHighLevelInterrupt(void)函数中均设置断点时,结果断点均没有触发。

同样的情况发生在设置Edge及Cap时,均无法进入HET高低中断。。。我设置的时钟中断均能正常进入。

请问还需设置哪里才能正常的进入HET的中断?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

用HCG生成的代码,配置如下图所示

我DEBUG时,PIN3的PWM波形正常,

但在void hetLowLevelInterrupt(void)以及void hetHighLevelInterrupt(void)函数中均设置断点时,结果断点均没有触发。

同样的情况发生在设置Edge及Cap时,均无法进入HET高低中断。。。我设置的时钟中断均能正常进入。

请问还需设置哪里才能正常的进入HET的中断?

Hi Forever,

有没有打开CPU的全局中断呢?

如果使用的是CCS的话,直接调用编译器的内嵌函数_enable_interrupts();就可以了。

Hi Forever,

噢,这样啊...

还是建议你升级到CCS V5.3,比CCS V4强大不少。

如果不习惯新的界面,那么可以考虑单独升级TI ARM Compiler, 目前最新应该是V5.0.3.

刚才确认了一下,抱歉,应该是HALCoGen生成的代码不完整所致。

请参考附件的例程。

原因是pwmEnableNotification();函数中只做了清Int Flag的动作,而没有真正去打开中断。

打开方法如下(仅针对HALCoGen生成的代码):

在pwmEnableNotification()函数中加入以下代码:

这段代码打开了Het指令中对应Duty和Period的中断使能位。

我加入了一个关掉中断的函数,在sys_main.c中,pwmDisableNotification();

附件例程是CCS V5.3基于TI ARM Compiler V5.0.3的,如果你无法直接打开,那么就把源文件导入你的工程中即可。

Hi Forever,

抱歉刚没注意你的描述。

这样的话,可能要仔细看一下设置了。

如果能够确认其他HALCoGen内部的设置(clock tree, oscillator, het clock等)都没有问题的话, 我们仔细看一下HET的代码吧。

PWM0的周期对应的更新指令是第42条指令,你可以打开het.c源文件来查看:

const hetINSTRUCTION_t hetPROGRAM[] 这个数组的内容。

找到第42条指令,如图:

这里的Data段,319872U就相当于比较寄存器的值。

我们需要把它右移7bit,得到真正的(周期值 - 1)。

319872U >>7U = 2499

周期是2499+1= 2500个LR clock.

根据你前面的描述,你的LR Clock设置为400ns。

即周期为1000us。

所以,请你看一下,是不是这个数字有问题?如果不是319872U或者比较接近的值,那么说明这个值错了。

我尝试用的是3000us做的周期

HCG生成的代码如下:

/* MOV64: PWM 0 -> Period Update

* - Instruction = 42

* - Next instruction = 3

* - Conditional next instruction = 41

* - Interrupt = 2

* - Pin = na

*/

{

/* Program */

0x00003102U,

/* Control */

(0x00029006U | 0x00000000U),

/* Data */

959872U,

/* Reserved */

0x00000000U

},

按你所说,959872U右移7位为7499,乘以400ns,也为3000us,与HCG设置一致。

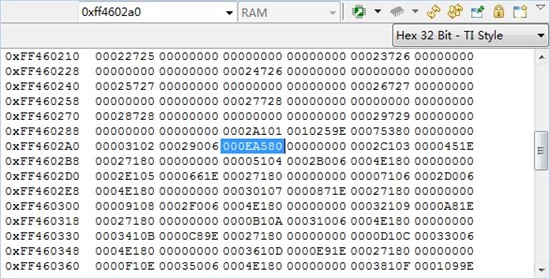

DEBUG时,看MEMORY如图,也与设置一致。

但示波器观察针脚波形时,周期就是为12ms,4倍的关系。。。

Hi Forever,

看来还是系统时钟的配置问题了。

先到HALCoGen的[Clock Tree]选项卡来确认VCLK2的输出,这个时钟是HET的基本时钟源。

默认情况下是80MHz,请查看是否正确。

再到[Global Clock Module]选项卡里面查看VCLK2的预分频设置。

但是一般情况下,HALCoGen是支持内部参考的,也就是说,如果这里改动了,那么HET选项卡中也会相应的改变。

如果您的HALCoGen不能做到这一点,可能是版本过低,请更新。

如果这两处都没有错,那么我觉得就是生成的代码与配置不一致。

可以深入代码中去查看寄存器的设置是否正确,当然这样比较浪费时间。

比较方便的办法就是用HALCoGen重新配置一个全新的工程,看看问题是否还在。