/* --COPYRIGHT--,BSD_EX

* Copyright (c) 2012, Texas Instruments Incorporated

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*******************************************************************************

*

* MSP430 CODE EXAMPLE DISCLAIMER

*

* MSP430 code examples are self-contained low-level programs that typically

* demonstrate a single peripheral function or device feature in a highly

* concise manner. For this the code may rely on the device's power-on default

* register values and settings such as the clock configuration and care must

* be taken when combining code from several examples to avoid potential side

* effects. Also see www.ti.com/grace for a GUI- and www.ti.com/msp430ware

* for an API functional library-approach to peripheral configuration.

*

* --/COPYRIGHT--*/

//******************************************************************************

// MSP430F552x Demo - Software Toggle P1.1 with 12MHz DCO

//

// Description: Toggle P1.1 by xor'ing P1.1 inside of a software loop.

// ACLK is rought out on pin P1.0, SMCLK is brought out on P2.2, and MCLK

// is brought out on pin P7.7.

// ACLK = REFO = 32kHz, MCLK = SMCLK = 12MHz

//

// MSP430F552x

// -----------------

// /|\| |

// | | P1.0|-->ACLK

// --|RST P7.7|-->MCLK

// | P2.2|-->SMCLK

// | |

// | P1.1|-->Port Pin

//

// Bhargavi Nisarga

// Texas Instruments Inc.

// April 2009

// Built with CCSv4 and IAR Embedded Workbench Version: 4.21

//******************************************************************************

#include <msp430.h>

* Copyright (c) 2012, Texas Instruments Incorporated

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*******************************************************************************

*

* MSP430 CODE EXAMPLE DISCLAIMER

*

* MSP430 code examples are self-contained low-level programs that typically

* demonstrate a single peripheral function or device feature in a highly

* concise manner. For this the code may rely on the device's power-on default

* register values and settings such as the clock configuration and care must

* be taken when combining code from several examples to avoid potential side

* effects. Also see www.ti.com/grace for a GUI- and www.ti.com/msp430ware

* for an API functional library-approach to peripheral configuration.

*

* --/COPYRIGHT--*/

//******************************************************************************

// MSP430F552x Demo - Software Toggle P1.1 with 12MHz DCO

//

// Description: Toggle P1.1 by xor'ing P1.1 inside of a software loop.

// ACLK is rought out on pin P1.0, SMCLK is brought out on P2.2, and MCLK

// is brought out on pin P7.7.

// ACLK = REFO = 32kHz, MCLK = SMCLK = 12MHz

//

// MSP430F552x

// -----------------

// /|\| |

// | | P1.0|-->ACLK

// --|RST P7.7|-->MCLK

// | P2.2|-->SMCLK

// | |

// | P1.1|-->Port Pin

//

// Bhargavi Nisarga

// Texas Instruments Inc.

// April 2009

// Built with CCSv4 and IAR Embedded Workbench Version: 4.21

//******************************************************************************

#include <msp430.h>

int main(void)

{

volatile unsigned int i;

{

volatile unsigned int i;

WDTCTL = WDTPW+WDTHOLD; // Stop WDT

P1DIR |= BIT1; // P1.1 output

P1DIR |= BIT1; // P1.1 output

P1DIR |= BIT0; // ACLK set out to pins

P1SEL |= BIT0;

P2DIR |= BIT2; // SMCLK set out to pins

P2SEL |= BIT2;

P7DIR |= BIT7; // MCLK set out to pins

P7SEL |= BIT7;

P1SEL |= BIT0;

P2DIR |= BIT2; // SMCLK set out to pins

P2SEL |= BIT2;

P7DIR |= BIT7; // MCLK set out to pins

P7SEL |= BIT7;

UCSCTL3 |= SELREF_2; // Set DCO FLL reference = REFO

UCSCTL4 |= SELA_2; // Set ACLK = REFO

UCSCTL4 |= SELA_2; // Set ACLK = REFO

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_5; // Select DCO range 24MHz operation

UCSCTL2 = FLLD_1 + 374; // Set DCO Multiplier for 12MHz

// (N + 1) * FLLRef = Fdco

// (374 + 1) * 32768 = 12MHz

// Set FLL Div = fDCOCLK/2

__bic_SR_register(SCG0); // Enable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_5; // Select DCO range 24MHz operation

UCSCTL2 = FLLD_1 + 374; // Set DCO Multiplier for 12MHz

// (N + 1) * FLLRef = Fdco

// (374 + 1) * 32768 = 12MHz

// Set FLL Div = fDCOCLK/2

__bic_SR_register(SCG0); // Enable the FLL control loop

// Worst-case settling time for the DCO when the DCO range bits have been

// changed is n x 32 x 32 x f_MCLK / f_FLL_reference. See UCS chapter in 5xx

// UG for optimization.

// 32 x 32 x 12 MHz / 32,768 Hz = 375000 = MCLK cycles for DCO to settle

__delay_cycles(375000);

// Loop until XT1,XT2 & DCO fault flag is cleared

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

while(1)

{

P1OUT ^= BIT1; // Toggle P1.1

__delay_cycles(600000); // Delay

}

}

// changed is n x 32 x 32 x f_MCLK / f_FLL_reference. See UCS chapter in 5xx

// UG for optimization.

// 32 x 32 x 12 MHz / 32,768 Hz = 375000 = MCLK cycles for DCO to settle

__delay_cycles(375000);

// Loop until XT1,XT2 & DCO fault flag is cleared

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

while(1)

{

P1OUT ^= BIT1; // Toggle P1.1

__delay_cycles(600000); // Delay

}

}

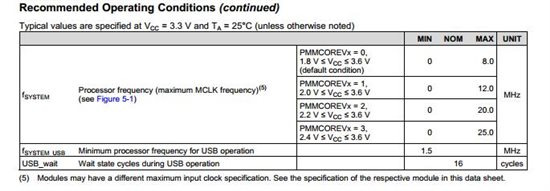

上面官方程序 时钟是12M,

为何没有提升内核电压,不解