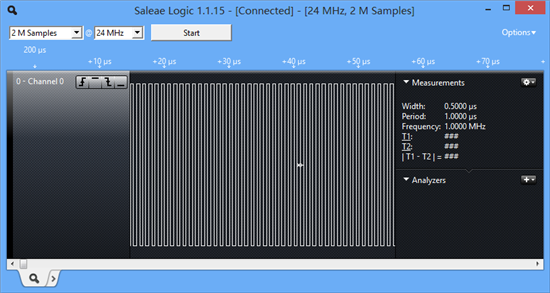

1MHz:

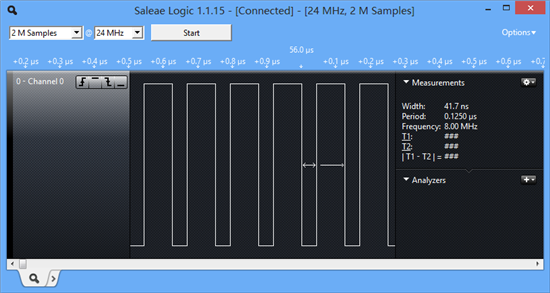

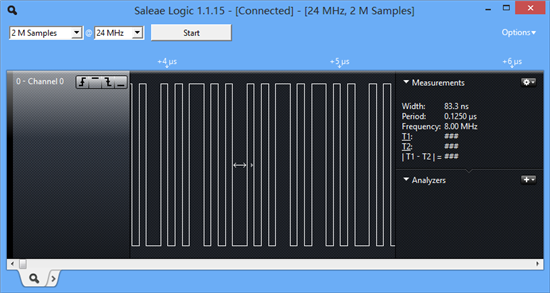

8MHz:

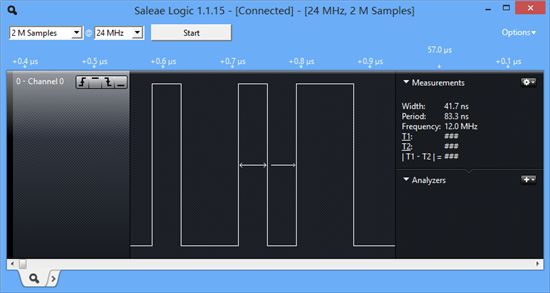

12MHz:

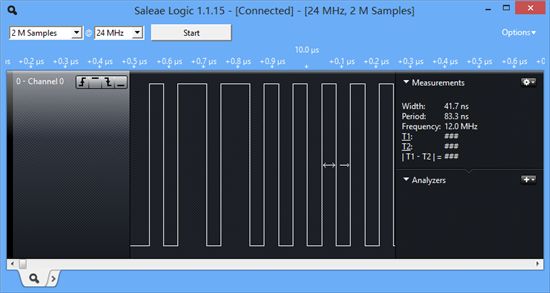

20MHz:

输出的是MCLK,用的是F5529官方例程的库.

#include <msp430.h>

#include "F5xx_F6xx_Core_Lib/HAL_PMM.h"

#include "F5xx_F6xx_Core_Lib/HAL_UCS.h"

int main(void)

{

volatile unsigned int i;

WDTCTL = WDTPW+WDTHOLD;

SetVCore(PMMCOREV_3);

P1DIR |= BIT1;

P1DIR |= BIT0;

P1SEL |= BIT0;

P3DIR |= BIT4;

P3SEL |= BIT4;

Init_FLL_Settle(20000, 610);

while(1)

{

P1OUT ^= BIT1; // Toggle P1.1

__delay_cycles(600000); // Delay

}

}