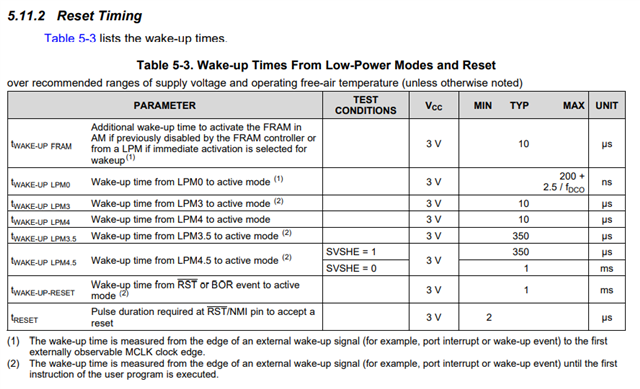

我目前看波形发现 芯片掉电到1.4V后,重现上电到跑进程序需要20ms左右的时间,有没有办法可以缩短上电进入程序的时间

int main(void)

{

Init_MCU();

Init_CLOCKS();

// SFRRPCR=0x000c;

P1SEL0 |= BIT2 | BIT3;

CE_7100_SET_OUT;

CE_7100_OUT_0;

CE_7100_OUT_1;CE_7100_OUT_0;

SYSCFG0 = FRWPPW | DFWP;

if(Write_flag.mode == cmd03nack)

Write_flag.count.CMD03 ++;

if(Write_flag.count.CMD03 == 2)

Write_flag.mode = normal;

if(Write_flag.mode != cmd03nack)

Init_IIC(Box_ID);

//Tim初始化

g_sn_change.tim_count=0; //clear

g_sn_change.Check_ID0105_flag=0;

g_sn_change.VDD_START_FLAG=0;

if(attest_flag==5)

{

Init_TIM(); //关闭TIM

TA0CTL |= TASSEL_2+MC_1+ID_2; //设置定时器计数模式开启

TA0CCTL0 = CCIE;

g_sn_change.tim_count=0;

g_sn_change.Check_ID0105_flag==1;

}

else if(attest_flag!=6)

{

Init_TIM(); //关闭TIM

attest_flag=0;

}

Change_ID=ID_BUF[ID_NUM]; //每次上电,确认当前码表的ID

DATA_7100_SET_OUT;

DATA_7100_OUT_0;

// CE_7100_SET_OUT;

CLK_7100_SET_OUT;

CLK_7100_OUT_0;

CE_7100_OUT_0;

// delay_us(100);

CE_7100_OUT_1;CE_7100_OUT_0;

// if(CJ7100_start_flag==1)

// {

// VDD_7100_SET_OUT;

// memset(Check_cj7100sn, 0, sizeof(Check_cj7100sn));

// while(CJ7100_start_flag==1) //7100数据异常,重新debug写码

// {

// VDD_7100_OUT_0;delay_ms(20); CJ7100_DEBUG_RST();

//

// f_7100_SN();

// if(strncmp(FRAM_write+0x440,Check_cj7100sn,12)==0)

// {

// CJ7100_start_flag=0;

// }

// else {

// CJ7100_start_flag=1;

// }

// }

// }

SYSCFG0 = FRWPPW | PFWP | DFWP;

while (1)

{

}

}