我需要采集15路脉冲信号的周期并计算每路脉冲的上升沿个数

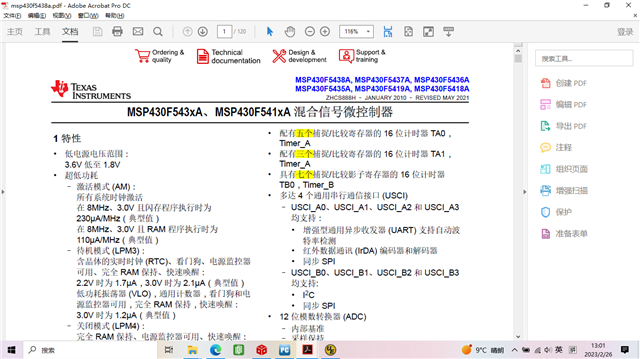

所以我在430产品线中选择了5438A

刚好有15路捕获

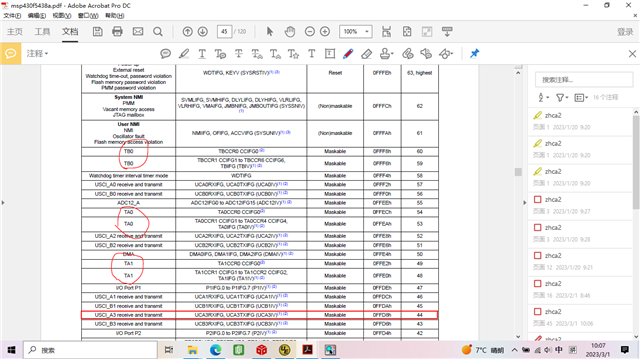

以timerA0为例 可以捕获5路脉冲信号

不过CCR0是有独立的中断的,CCR1至CCR4是公用一个中断信号的

timerA1情况类似,CCR0有独立中断,CCR1到CCR2公用一个中断信号

timerB也是这样的,CCR0有独立中断,CCR1到CCR6公用一个中断信号

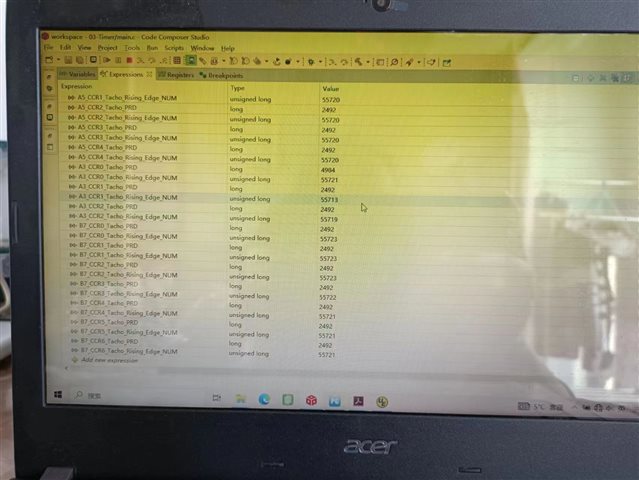

各个timer的时钟都是用的XT2高速时钟分频得到(做32分频),目前XT2是配置了一颗16MHz的晶体,

我要采集的信号周期最小为5mS左右,测试时我将5mS周期的PWM波同时连接到15路捕获输入引脚 没有让430进入低功耗模式 这是我测试的结果

可以看到,脉冲计数通道间有一些差异

当然,我的这个测试有些极端,一路5mS的PWM同时连接到了15路捕获输入引脚,实际的信号源边沿是有先后的

问题1.既然存在公用中断信号,而且3个timer的中断优先级也有高低,那是不是一定会存在丢脉冲边沿的情况呢?

问题2.如果提高XT2的主频为24MHz,使用高精度、低温漂的有源晶振,并且主时钟、子时钟均使用这个24MHz的时钟,各timer的计数时钟由子时钟分频得到,检测时丢脉冲边沿的情况会有改善吗?

提高主频,目的是想减小处理器中断函数处理的时间;采用有源晶振替代目前的晶体是想提高时钟精度

问题3.因为数据要通过串口传出去,这样在引入串口发送中断的话,检测时丢脉冲的边沿的可能性是不是会加大