Other Parts Discussed in Thread: MSP-EXP430FR5994

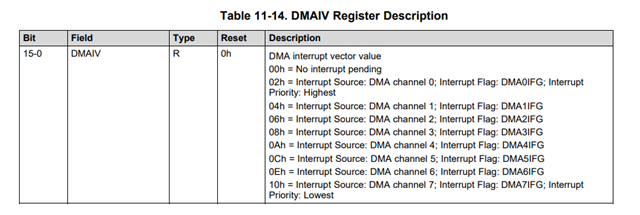

使用DMA通道0和1,设置中断使能,直接复制的官方例程中的DMA中断服务程序,应该是需要两个,DMA0的和DMA1的,官方例程只有一种,如何配置才能分别触发通道0和1的中断,进入中断服务程序,官方中断服务程序如下

//------------------------------------------------------------------------------

// DMA Interrupt Service Routine

//------------------------------------------------------------------------------

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=DMA_VECTOR

__interrupt void DMA_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(DMA_VECTOR))) DMA_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(DMAIV,16))

{

case 0: break;

case 2: // DMA0IFG = DMA Channel 0

P1OUT ^= BIT0; // Toggle P1.0 - PLACE BREAKPOINT HERE AND CHECK DMA_DST VARIABLE

break;

case 4: break; // DMA1IFG = DMA Channel 1

case 6: break; // DMA2IFG = DMA Channel 2

case 8: break; // DMA3IFG = DMA Channel 3

case 10: break; // DMA4IFG = DMA Channel 4

case 12: break; // DMA5IFG = DMA Channel 5

case 14: break; // DMA6IFG = DMA Channel 6

case 16: break; // DMA7IFG = DMA Channel 7

default: break;

}

}