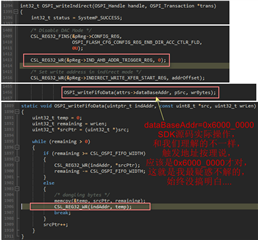

1Ch OSPI_IND_AHB_ADDR_TRIGGER_REG Indirect trigger address register 0FC4 001Ch

24h OSPI_REMAP_ADDR_REG Address remapping register 0FC4 0024h

80h OSPI_INDIRECT_TRIGGER_ADDR_RANGE_REG Indirect trigger address range register 0FC4 0080h

OSPI_REMAP_ADDR_REG,应该时内存映射地址设置,0x6000_0000

OSPI_IND_AHB_ADDR_TRIGGER_REG,应该是间接读写Flash时的触发地址

OSPI_INDIRECT_TRIGGER_ADDR_RANGE_REG,应该是间接读写Flash时的触发地址范围

按我的理解,比如我设置内存映射地址为0x6000_0000,触发地址为0x7000_1000,触发地址范围为0x1000,

那么我在读写Flash时,如果读写0x7000_1200,就可以读写Flash的0x6000_1200空间,但事实是,设置这些寄存器,没有任何反应

看TI公司官方SDK源码发现,

CSL_REG32_WR(&pReg->IND_AHB_ADDR_TRIGGER_REG, 0);

CSL_REG32_WR(&pReg->INDIRECT_TRIGGER_ADDR_RANGE_REG, OSPI_utilLog2(128));

读写Flash时,只能读写0x6000_0000,才能操作SRAM Fifo,实现间接读写功能,请专家们帮忙解释一下,谢谢