我在调试PWM功能时注意到这个问题,调用SysCtlClockSet函数设置时钟频率时,

SYSCTL_SYSDIV_4表示PLL分频4倍,即200M/4=50M,

当我改成SYSCTL_SYSDIV_2时,测得的时钟是66.67M,

改成SYSCTL_SYSDIV_3,时钟还是66.67M,

改成SYSCTL_SYSDIV_1,变成12.5M了。

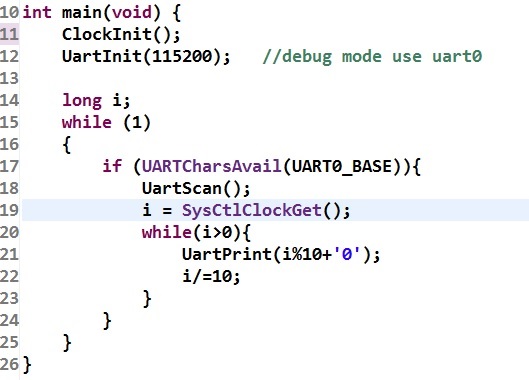

后来我专门写了个程序打印

ClockInit仅仅是调用SysCtlClockSet,打印结果与测试结果一致。

以下是sysctl.h头文件内容

试验下来似乎只有1和2有BUG。