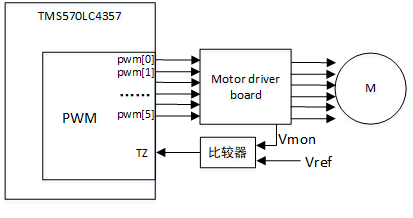

您好,在使用TMS570LC4357中PWM驱动无刷三相电机时,使用模拟比较芯片对电机驱动板电压进行监控,并连接至PWM的TZ输入上,具体如下示意图。

经过示波器抓取信号发现,模拟比较器输出给PWM TZ的信号上有毛刺,且对应每一个PWM周期中,毛刺出现位置不固定,想通过PWM内数字比较模块DC中的滤波功能对TZ上的毛刺进行过滤。但是经过尝试后仍有问题,具体如下:

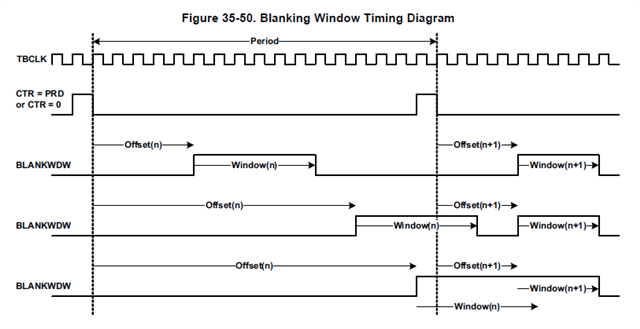

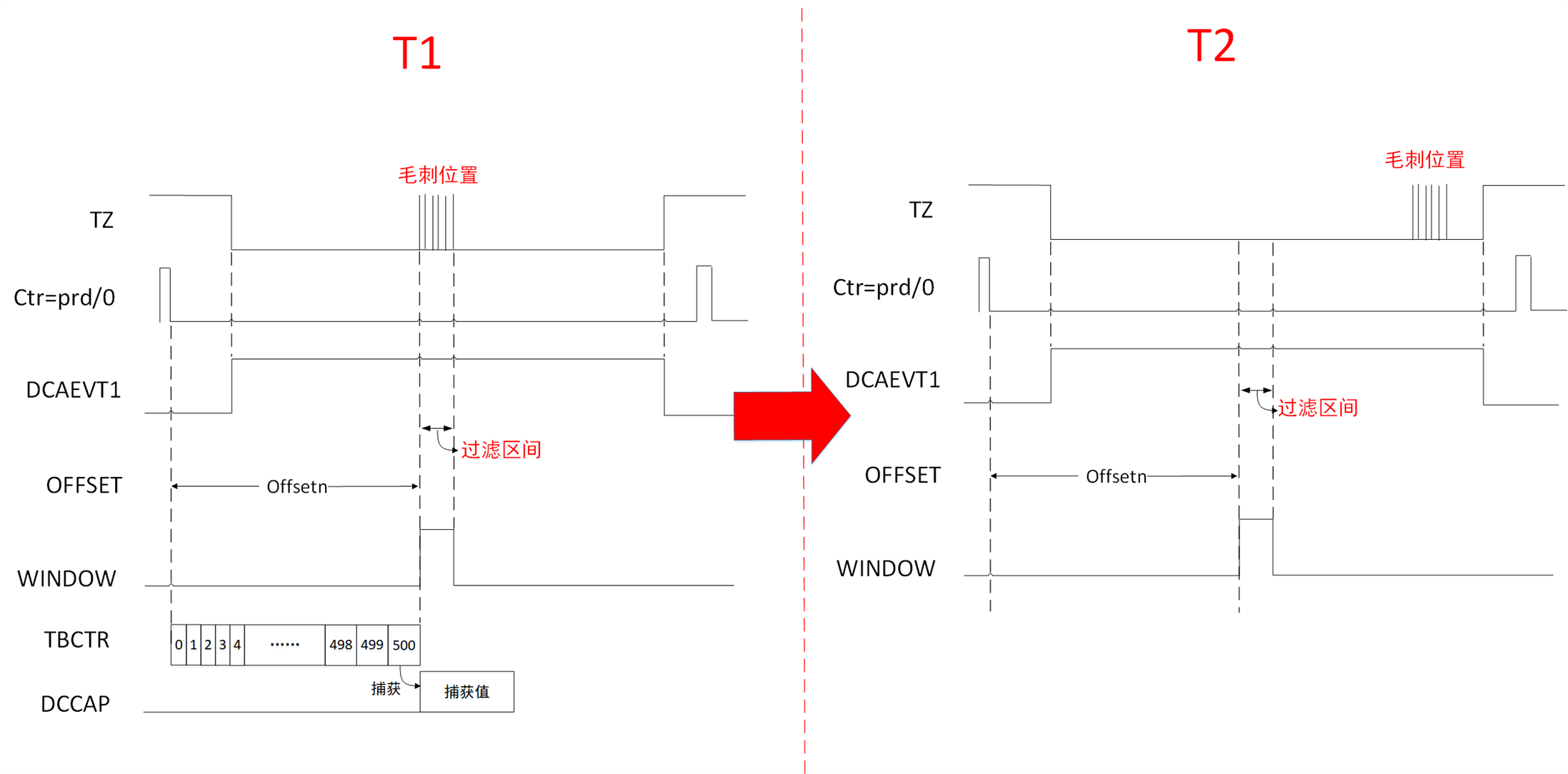

假设下图中T1和T2是两个相邻的PWM周期(T2在T1时刻后),根据TMS570LC4357 PWM模块DC章节的解释:

- WINDOW计数器是在OFFSET计数器向下计数至0后开始计数

- WINDOW区间内的毛刺会被过滤

- DCCAP寄存器可捕获DCEVFILT事件发生时,时基计数器的值。

那么基于以上三点,假设在T1时刻,毛刺出现在TZ信号中间处左右,首先软件需要设置开启DC捕获功能,读取DCCAP寄存器的值,用DCCAP中捕获时基计数器的值来设置下图中OFFSET长度,同时根据毛刺宽度设置WINDOW区间,使得WINDOW过滤区间覆盖毛刺出现的区域,达到过滤毛刺的目的。但是如果在下一个周期时(T2时刻),TZ信号上毛刺出现的位置发生了改变,例如毛刺出现在TZ后部分区域,此时由于T1时刻配置的offsetn和window无法满足T2时刻,导致T1时刻配置的过滤区间无法过滤T2时刻的毛刺。

疑问:

1,PWM 模块中DC过滤毛刺功能是否只支持过滤位置固定出现在TZ信号上的毛刺?(例如上图中T1时刻的毛刺和T2时刻的毛刺如果出现在相同位置,此时如果用上述方法,则可以根据T1时刻捕获的值,合理设置上述几个参数,使得在T2时刻毛刺被滤除。但是如果毛刺出现在不同位置,按照上述算法,则无法过滤。)

2,如果每次毛刺出现的宽度不一致,软件应该如何动态调整WINDOW计数器的值,使其覆盖毛刺出现的区域?(不可能每次都用示波器测量毛刺宽度,太繁琐。)