Part Number: DRV8163S-Q1EVM

Hello Team

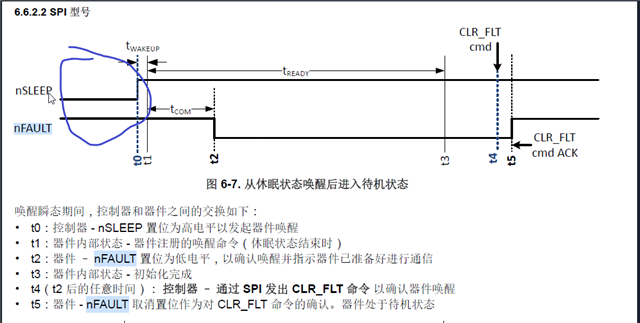

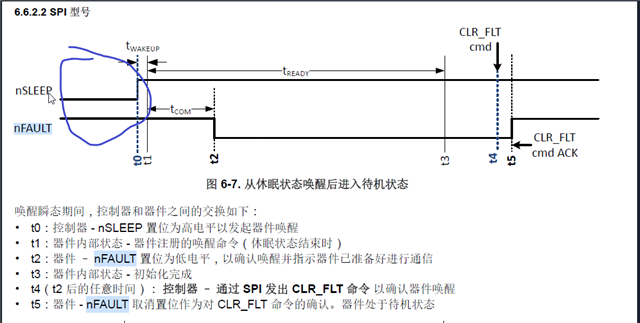

上电时,Nsleep 默认为低,nFault为上拉5V,监控上电时,Nsleep一直为低,但是nFault拉高5ms后拉低,为什么会这样?按照Datasheet时序图,Sleep为低时,nFault应该一直为高才对,

希望尽快得到答复

感谢

David

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DRV8163S-Q1EVM

Hello Team

上电时,Nsleep 默认为低,nFault为上拉5V,监控上电时,Nsleep一直为低,但是nFault拉高5ms后拉低,为什么会这样?按照Datasheet时序图,Sleep为低时,nFault应该一直为高才对,

希望尽快得到答复

感谢

David