hi TI:

As for the following problems, we plan to launch FAR. FAE suggests to review the application schematic in E2E forum first. Please help analyze the following problems and review our design.

Problem phenomenon: in the DVT stage, there are 4 cases of motor failure to drive the problem, the motor driver IC (MCF8316C-Q1) single consumption of 3PCS (bit number: U8,U5,U9), 84 complete machines, the bad ratio: 4/84x3=4/252;

Abnormal prototype: 1# 2# is bad U8, 3# 4# is bad U5, and 1# 2# adverse phenomena are consistent. 3# 4# adverse phenomena are consistent.

Phenomenon analysis:

1, 1# 2# test peripheral voltage and signal, the DVDD voltage inside the chip has no output; Registers inside the chip cannot be accessed and written; (Measurement Vm:12V; AVDD: 3.3V; DVDD: 0V; Vbk:0.5V)

2, 3# 4# test peripheral voltage and signal, voltage ripple, voltage accuracy, monotonic power on and off all meet the requirements, no peripheral design anomalies are found, but the internal register can not be accessed and written; (Measurement Vm:12V; AVDD: 3.3V; DVDD: 3.3V; Vbk:3.3V)

3, 1# 2# 3# 4# After cross-verification, the bad phenomenon follows the chip (the abnormal chip replaces the normal chip after the whole machine works normally, the abnormal is stuck on the normal board and the abnormal occurs again)

4, No abnormality was found in the impedance test of the normal chip

failure chip MARK:

TI 468 A77G G4 1EC6D

TI 468 A77G G4 191D7

TI 468 A77G G4 1B2C5

TI 468 A77G G4 196E1

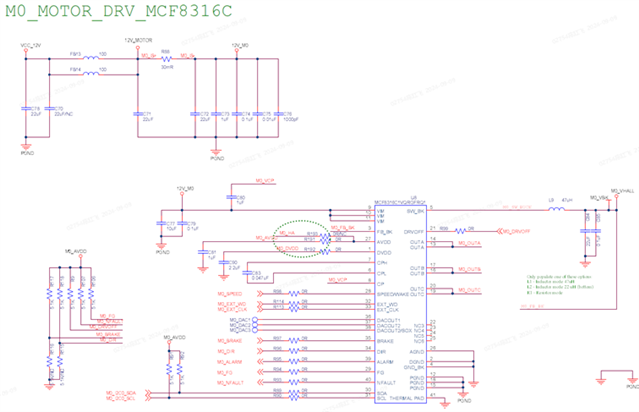

Attached is the schematic diagram and register config!

thanks

Fred

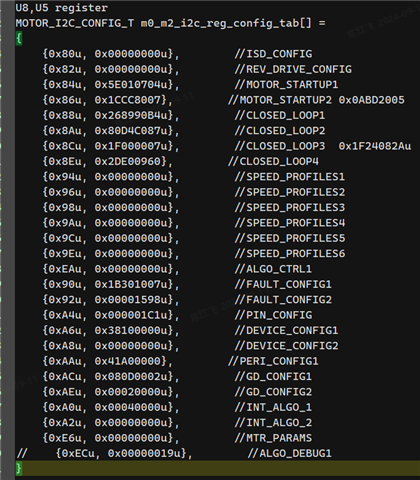

U8,U5 register

MOTOR_I2C_CONFIG_T m0_m2_i2c_reg_config_tab[] =

{

{0x80u, 0x00000000u}, //ISD_CONFIG

{0x82u, 0x00000000u}, //REV_DRIVE_CONFIG

{0x84u, 0x5E010704u}, //MOTOR_STARTUP1

{0x86u, 0x1CCC8007}, //MOTOR_STARTUP2 0x0ABD2005

{0x88u, 0x268990B4u}, //CLOSED_LOOP1

{0x8Au, 0x80D4C087u}, //CLOSED_LOOP2

{0x8Cu, 0x1F000007u}, //CLOSED_LOOP3 0x1F24082Au

{0x8Eu, 0x2DE00960}, //CLOSED_LOOP4

{0x94u, 0x00000000u}, //SPEED_PROFILES1

{0x96u, 0x00000000u}, //SPEED_PROFILES2

{0x98u, 0x00000000u}, //SPEED_PROFILES3

{0x9Au, 0x00000000u}, //SPEED_PROFILES4

{0x9Cu, 0x00000000u}, //SPEED_PROFILES5

{0x9Eu, 0x00000000u}, //SPEED_PROFILES6

{0xEAu, 0x00000000u}, //ALGO_CTRL1

{0x90u, 0x1B301007u}, //FAULT_CONFIG1

{0x92u, 0x00001598u}, //FAULT_CONFIG2

{0xA4u, 0x000001C1u}, //PIN_CONFIG

{0xA6u, 0x38100000u}, //DEVICE_CONFIG1

{0xA8u, 0x00000000u}, //DEVICE_CONFIG2

{0xAAu, 0x41A00000}, //PERI_CONFIG1

{0xACu, 0x080D0002u}, //GD_CONFIG1

{0xAEu, 0x00020000u}, //GD_CONFIG2

{0xA0u, 0x00040000u}, //INT_ALGO_1

{0xA2u, 0x00000000u}, //INT_ALGO_2

{0xE6u, 0x00000000u}, //MTR_PARAMS

// {0xECu, 0x00000019u}, //ALGO_DEBUG1

}

U9 register

MOTOR_I2C_CONFIG_T m1_i2c_reg_config_tab[] =

{

{0x80u, 0x00000000u}, //ISD_CONFIG

{0x82u, 0x00000000u}, //REV_DRIVE_CONFIG

{0x84u, 0x5E00C544u}, //MOTOR_STARTUP1

{0x86u, 0x32AC8007u}, //MOTOR_STARTUP2

{0x88u, 0x3E8B10B4u}, //CLOSED_LOOP1

{0x8Au, 0xA0D4B538u}, //CLOSED_LOOP2

{0x8Cu, 0x5420F008u}, //CLOSED_LOOP3

{0x8Eu, 0x32900258u}, //CLOSED_LOOP4

{0x94u, 0x00000000u}, //SPEED_PROFILES1

{0x96u, 0x00000000u}, //SPEED_PROFILES2

{0x98u, 0x00000000u}, //SPEED_PROFILES3

{0x9Au, 0x00000000u}, //SPEED_PROFILES4

{0x9Cu, 0x00000000u}, //SPEED_PROFILES5

{0x9Eu, 0x00000000u}, //SPEED_PROFILES6

{0xEAu, 0x00000000u}, //ALGO_CTRL1

{0x90u, 0x23B81007u}, //FAULT_CONFIG1

{0x92u, 0x00001598u}, //FAULT_CONFIG2

{0xA4u, 0x000001c1u}, //PIN_CONFIG

{0xA6u, 0x38100000u}, //DEVICE_CONFIG1

{0xA8u, 0x00000000u}, //DEVICE_CONFIG2

{0xAAu, 0x41E00000u}, //PERI_CONFIG1

{0xACu, 0x080d0002u}, //GD_CONFIG1

{0xAEu, 0x00020000u}, //GD_CONFIG2

{0xA0u, 0x00000000u}, //INT_ALGO_1

{0xA2u, 0x00000000u}, //INT_ALGO_2

{0xE6u, 0x00000000u}, //MTR_PARAMS

};

Fred