Part Number: TMS320F280049

有没有前辈帮忙看看配置是否有问题。

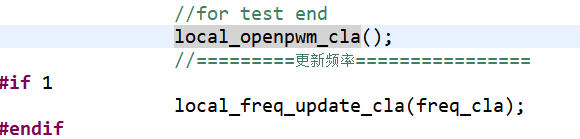

环路是在CLA中运行的,环路运行结束后打开PWM随后更新频率

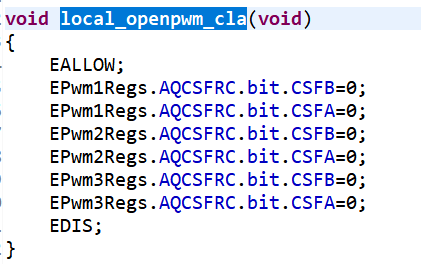

每次更新频率前都执行一次 local_openpwm_cla()

更新频率

您好,

您参考的是本文档吗?:www.ti.com/.../sprad15.pdf

本文档展示了 SR 侧而非初级侧的第三相问题。 那些初级侧没有特殊要求。

另外、客户看到的异常问题是什么意思? 您能用一些图或其他图来详细说明一下吗?

此外、您能否以文本形式发送这些 EPWM 配置? 很难分析图像。

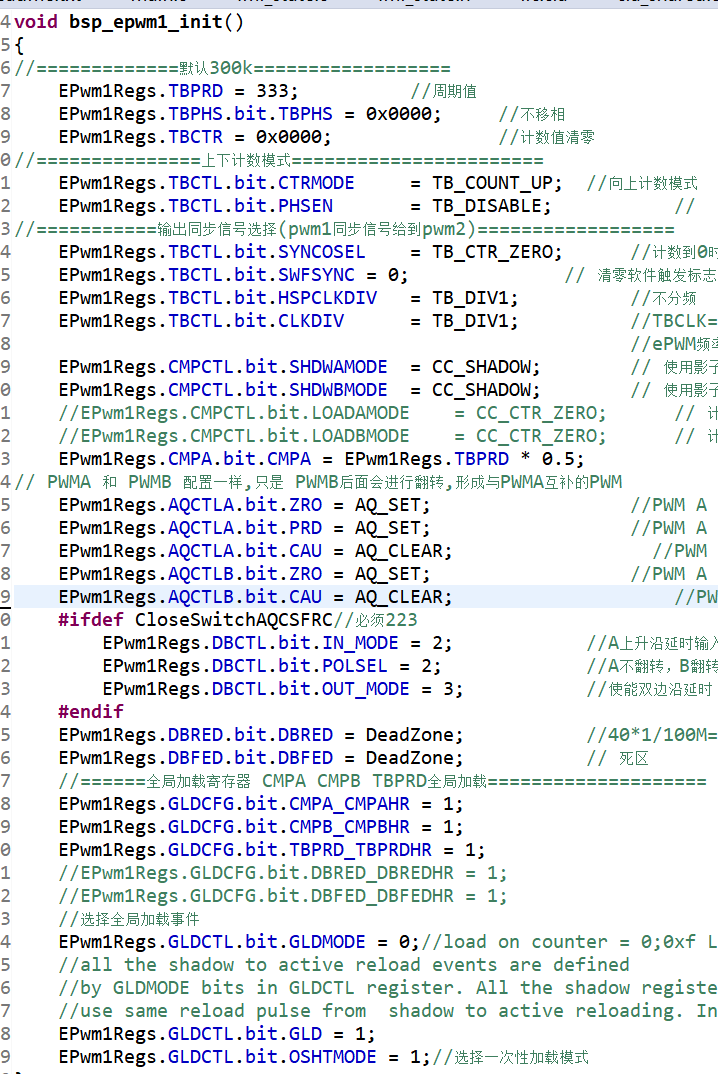

void bsp_epwm1_init()

{

//=============默认300k==================

EPwm1Regs.TBPRD = 333; //周期值

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; //不移相

EPwm1Regs.TBCTR = 0x0000; //计数值清零

//===============上下计数模式=======================

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; //向上计数模式

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; //

//===========输出同步信号选择(pwm1同步信号给到pwm2)==================

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; //计数到0时发出同步信号

EPwm1Regs.TBCTL.bit.SWFSYNC = 0; // 清零软件触发标志(初始状态)

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //不分频

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; //TBCLK=SYSCKOUT/(HSPCLKDIV*CLKDIV)=100MHz/(1*1)=100MHz

//ePWM频率=TBCLK/(2*TBPRD)=100M/(2*333)=150kHz

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // 使用影子寄存器

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // 使用影子寄存器

//EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // 计数到0更新

//EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // 计数到0更新

EPwm1Regs.CMPA.bit.CMPA = EPwm1Regs.TBPRD * 0.5; //初始化 CMP A= TBPRD/2 50%占空比

// PWMA 和 PWMB 配置一样,只是 PWMB后面会进行翻转,形成与PWMA互补的PWM

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; //PWM A 计数至0 时输出 高H

EPwm1Regs.AQCTLA.bit.PRD = AQ_SET; //PWM A 计数至0 时输出 高H

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; //PWM A 向上计数至CMP A 时输出 L

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET; //PWM A 计数至0 时输出 高H

EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; //PWM B 向上计数至CMP A 时输出 高H

#ifdef CloseSwitchAQCSFRC//必须223

EPwm1Regs.DBCTL.bit.IN_MODE = 2; //A上升沿延时输入源,B下降沿延时输入源

EPwm1Regs.DBCTL.bit.POLSEL = 2; //A不翻转,B翻转

EPwm1Regs.DBCTL.bit.OUT_MODE = 3; //使能双边沿延时

#endif

EPwm1Regs.DBRED.bit.DBRED = DeadZone; //40*1/100M=0.4us=400ns死区

EPwm1Regs.DBFED.bit.DBFED = DeadZone; // 死区

//======全局加载寄存器 CMPA CMPB TBPRD全局加载====================

EPwm1Regs.GLDCFG.bit.CMPA_CMPAHR = 1;

EPwm1Regs.GLDCFG.bit.CMPB_CMPBHR = 1;

EPwm1Regs.GLDCFG.bit.TBPRD_TBPRDHR = 1;

//EPwm1Regs.GLDCFG.bit.DBRED_DBREDHR = 1;

//EPwm1Regs.GLDCFG.bit.DBFED_DBFEDHR = 1;

//选择全局加载事件

EPwm1Regs.GLDCTL.bit.GLDMODE = 0;//load on counter = 0;0xf Load on GLDCTL2[GFRCLD] write

//all the shadow to active reload events are defined

//by GLDMODE bits in GLDCTL register. All the shadow registers

//use same reload pulse from shadow to active reloading. Individual LOADMODE bits are ignored.

EPwm1Regs.GLDCTL.bit.GLD = 1;

EPwm1Regs.GLDCTL.bit.OSHTMODE = 1;//选择一次性加载模式

}

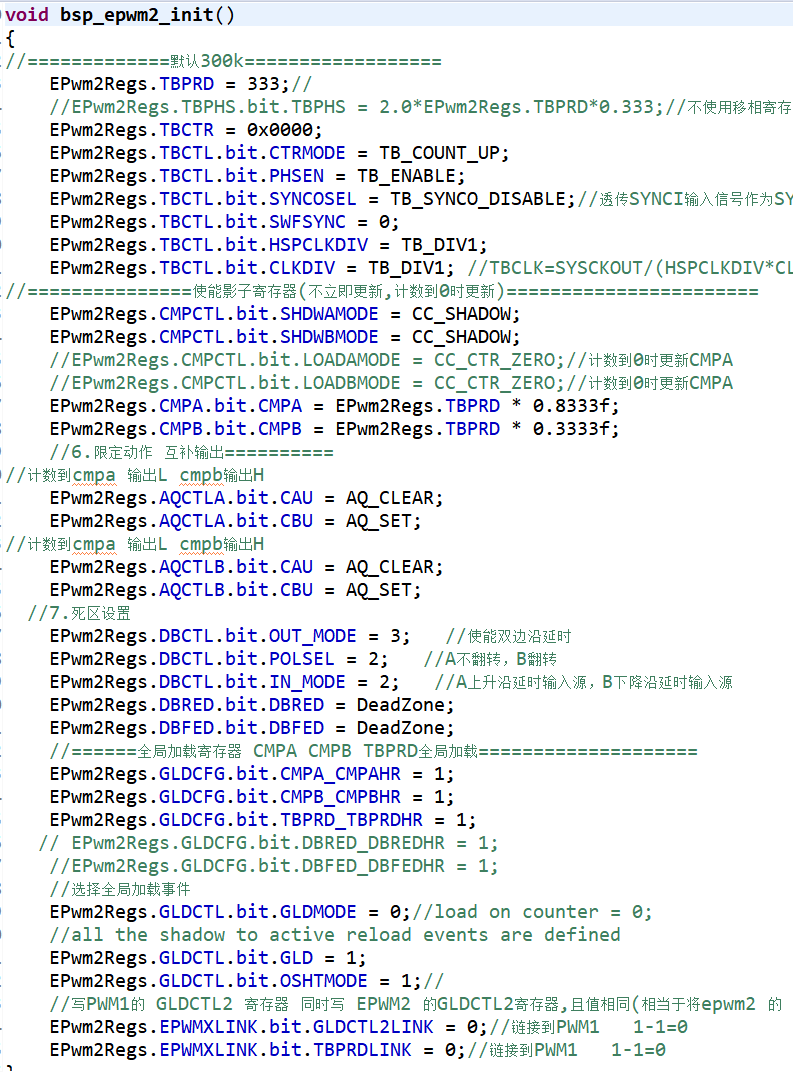

void bsp_epwm2_init()

{

//=============默认300k==================

EPwm2Regs.TBPRD = 333;//

//EPwm2Regs.TBPHS.bit.TBPHS = 2.0*EPwm2Regs.TBPRD*0.333;//不使用移相寄存器,使用CMP值移相

EPwm2Regs.TBCTR = 0x0000;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNCO_DISABLE;//透传SYNCI输入信号作为SYNCO输出

EPwm2Regs.TBCTL.bit.SWFSYNC = 0;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; //TBCLK=SYSCKOUT/(HSPCLKDIV*CLKDIV)=100MHz/(1*1)=100MHz

//===============使能影子寄存器(不立即更新,计数到0时更新)=======================

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

//EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;//计数到0时更新CMPA

//EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;//计数到0时更新CMPA

EPwm2Regs.CMPA.bit.CMPA = EPwm2Regs.TBPRD * 0.8333f;

EPwm2Regs.CMPB.bit.CMPB = EPwm2Regs.TBPRD * 0.3333f;

//6.限定动作 互补输出==========

//计数到cmpa 输出L cmpb输出H

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CBU = AQ_SET;

//计数到cmpa 输出L cmpb输出H

EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBU = AQ_SET;

//7.死区设置

EPwm2Regs.DBCTL.bit.OUT_MODE = 3; //使能双边沿延时

EPwm2Regs.DBCTL.bit.POLSEL = 2; //A不翻转,B翻转

EPwm2Regs.DBCTL.bit.IN_MODE = 2; //A上升沿延时输入源,B下降沿延时输入源

EPwm2Regs.DBRED.bit.DBRED = DeadZone;

EPwm2Regs.DBFED.bit.DBFED = DeadZone;

//======全局加载寄存器 CMPA CMPB TBPRD全局加载====================

EPwm2Regs.GLDCFG.bit.CMPA_CMPAHR = 1;

EPwm2Regs.GLDCFG.bit.CMPB_CMPBHR = 1;

EPwm2Regs.GLDCFG.bit.TBPRD_TBPRDHR = 1;

// EPwm2Regs.GLDCFG.bit.DBRED_DBREDHR = 1;

//EPwm2Regs.GLDCFG.bit.DBFED_DBFEDHR = 1;

//选择全局加载事件

EPwm2Regs.GLDCTL.bit.GLDMODE = 0;//load on counter = 0;

//all the shadow to active reload events are defined

EPwm2Regs.GLDCTL.bit.GLD = 1;

EPwm2Regs.GLDCTL.bit.OSHTMODE = 1;//

//写PWM1的 GLDCTL2 寄存器 同时写 EPWM2 的GLDCTL2寄存器,且值相同(相当于将epwm2 的 GLDCTL2寄存器链接到 EPWM1 的 GLDCTL2寄存器)

EPwm2Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;//链接到PWM1 1-1=0

EPwm2Regs.EPWMXLINK.bit.TBPRDLINK = 0;//链接到PWM1 1-1=0

}

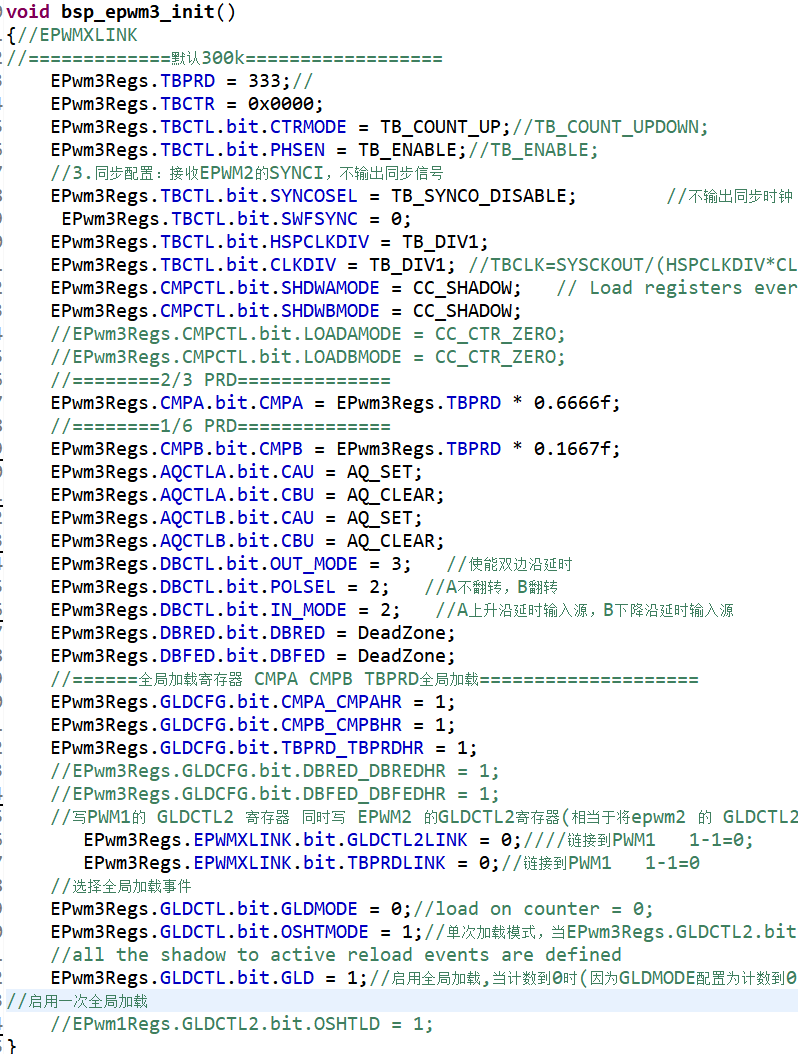

void bsp_epwm3_init()

{//EPWMXLINK

//=============默认300k==================

EPwm3Regs.TBPRD = 333;//

EPwm3Regs.TBCTR = 0x0000;

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//TB_COUNT_UPDOWN;

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE;//TB_ENABLE;

//3.同步配置:接收EPWM2的SYNCI,不输出同步信号

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNCO_DISABLE; //不输出同步时钟

EPwm3Regs.TBCTL.bit.SWFSYNC = 0;

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1; //TBCLK=SYSCKOUT/(HSPCLKDIV*CLKDIV)=100MHz/(1*1)=100MHz

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

//EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

//EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//========2/3 PRD==============

EPwm3Regs.CMPA.bit.CMPA = EPwm3Regs.TBPRD * 0.6666f;

//========1/6 PRD==============

EPwm3Regs.CMPB.bit.CMPB = EPwm3Regs.TBPRD * 0.1667f;

EPwm3Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm3Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm3Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm3Regs.DBCTL.bit.OUT_MODE = 3; //使能双边沿延时

EPwm3Regs.DBCTL.bit.POLSEL = 2; //A不翻转,B翻转

EPwm3Regs.DBCTL.bit.IN_MODE = 2; //A上升沿延时输入源,B下降沿延时输入源

EPwm3Regs.DBRED.bit.DBRED = DeadZone;

EPwm3Regs.DBFED.bit.DBFED = DeadZone;

//======全局加载寄存器 CMPA CMPB TBPRD全局加载====================

EPwm3Regs.GLDCFG.bit.CMPA_CMPAHR = 1;

EPwm3Regs.GLDCFG.bit.CMPB_CMPBHR = 1;

EPwm3Regs.GLDCFG.bit.TBPRD_TBPRDHR = 1;

//EPwm3Regs.GLDCFG.bit.DBRED_DBREDHR = 1;

//EPwm3Regs.GLDCFG.bit.DBFED_DBFEDHR = 1;

//写PWM1的 GLDCTL2 寄存器 同时写 EPWM2 的GLDCTL2寄存器(相当于将epwm2 的 GLDCTL2寄存器链接到 EPWM1 的 GLDCTL2寄存器)

EPwm3Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;////链接到PWM1 1-1=0;

EPwm3Regs.EPWMXLINK.bit.TBPRDLINK = 0;//链接到PWM1 1-1=0

//选择全局加载事件

EPwm3Regs.GLDCTL.bit.GLDMODE = 0;//load on counter = 0;

EPwm3Regs.GLDCTL.bit.OSHTMODE = 1;//单次加载模式,当EPwm3Regs.GLDCTL2.bit.OSHTLD = 1;时加载(达到加载条件时加载)

//all the shadow to active reload events are defined

EPwm3Regs.GLDCTL.bit.GLD = 1;//启用全局加载,当计数到0时(因为GLDMODE配置为计数到0作为全局加载事件)将所有影子寄存器加载到活动寄存器

//启用一次全局加载

//EPwm1Regs.GLDCTL2.bit.OSHTLD = 1;

}

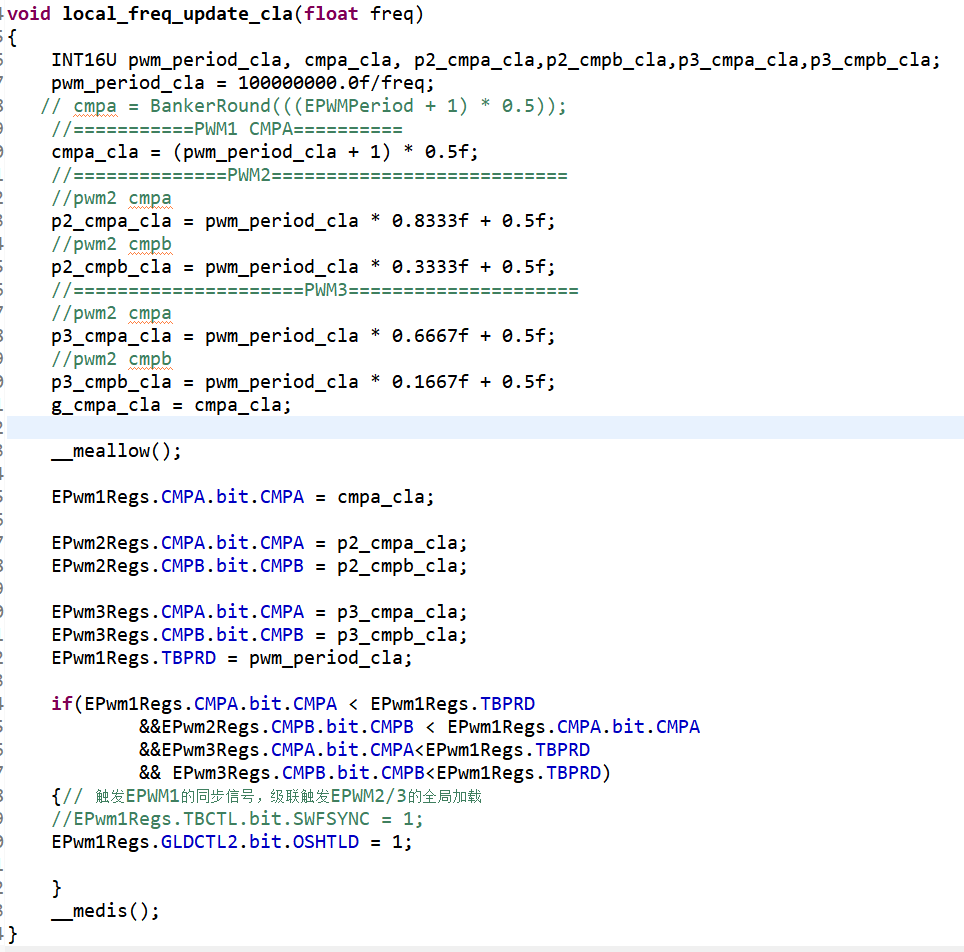

void local_freq_update_cla(float freq)

{

INT16U pwm_period_cla, cmpa_cla, p2_cmpa_cla,p2_cmpb_cla,p3_cmpa_cla,p3_cmpb_cla;

pwm_period_cla = 100000000.0f/freq;

// cmpa = BankerRound(((EPWMPeriod + 1) * 0.5));

//===========PWM1 CMPA==========

cmpa_cla = (pwm_period_cla + 1) * 0.5f;

//==============PWM2===========================

//pwm2 cmpa

p2_cmpa_cla = pwm_period_cla * 0.8333f + 0.5f;

//pwm2 cmpb

p2_cmpb_cla = pwm_period_cla * 0.3333f + 0.5f;

//=====================PWM3=====================

//pwm2 cmpa

p3_cmpa_cla = pwm_period_cla * 0.6667f + 0.5f;

//pwm2 cmpb

p3_cmpb_cla = pwm_period_cla * 0.1667f + 0.5f;

g_cmpa_cla = cmpa_cla;

__meallow();

//__mdebugstop();

EPwm1Regs.CMPA.bit.CMPA = cmpa_cla;

EPwm2Regs.CMPA.bit.CMPA = p2_cmpa_cla;

EPwm2Regs.CMPB.bit.CMPB = p2_cmpb_cla;

EPwm3Regs.CMPA.bit.CMPA = p3_cmpa_cla;

EPwm3Regs.CMPB.bit.CMPB = p3_cmpb_cla;

EPwm1Regs.TBPRD = pwm_period_cla;

if(EPwm1Regs.CMPA.bit.CMPA < EPwm1Regs.TBPRD&&EPwm2Regs.CMPB.bit.CMPB < EPwm1Regs.CMPA.bit.CMPA&&EPwm3Regs.CMPA.bit.CMPA<EPwm1Regs.TBPRD&& EPwm3Regs.CMPB.bit.CMPB<EPwm1Regs.TBPRD)

{

EPwm1Regs.GLDCTL2.bit.OSHTLD = 1;

}

__medis();

}您好,

我认为该配置在我看来是应用手册中使用的确切方法、即为全局加载配置一次性操作。 我想向客户推荐另一种方法。 对于初级侧三相交错型 LLC、我在所附的 pdf 文件中附加了两种 ISR 方法、可供您推荐给客户。 他们仍然可以保持 ePWM 器件/配置相同、但使用两个 ISR 来实现、这应该有助于解决他们面临的问题。 当 ISR 频率大于/小于开关频率时、即使频率阶跃发生变化、此方法也适用于这两种情况。

如果对此有任何疑问、请告诉我