Other Parts Discussed in Thread: TPS62130

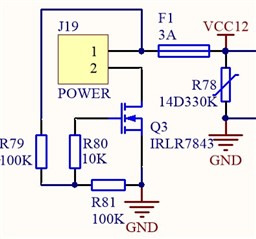

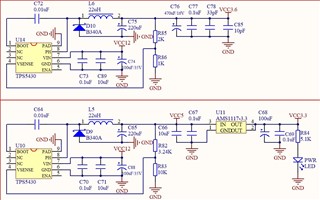

我的基本设计是DC12V输入,DC5V输出,再接LDO转DC3.3V输出,请教两个问题:

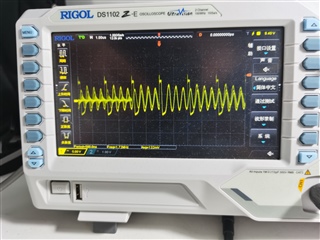

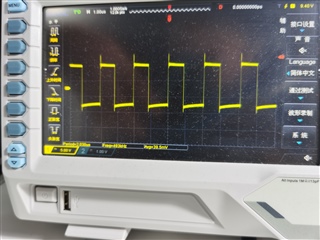

1、TPS5430电路是不是不能空载运行,调试过程中发现空载的情况下,正常工作一段时间后输出电压会不稳定,有跌落现象,boot脚波形也不是方波,而是如下图这种波形

或者

或者

请问这种现象是否正常?

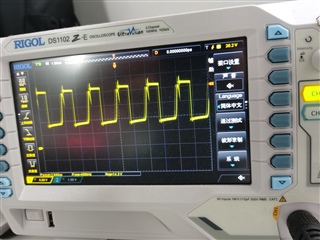

2、加入负载以后,负载正常工作,有些boot脚波形是方波如下图

但有部分芯片的boot脚波形不完全是方波,如下图

似乎是由于负载电流偏小造成的,请问如果负载偏小,应该调整哪个元件来使开关状态稳定在方波状态?

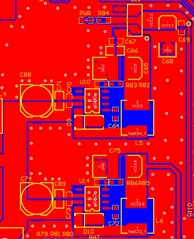

下图是我的layerout图,基本都是参照datasheet设计的,应该没什么问题吧?