之前发了一个帖子,自己没有理解,混淆了复位和断电两者的概念。

重新整理了下,问题描述如下:

在设计6678供电方案的时候发现,EVM板是通过FPGA来控制上电时序和断电时序的。

论坛上的一些经验帖说,是可以脱离控制芯片来设计供电时序的。因此在自己设计6678供电方案时,没有采用FPGA,只是通过TPS54620等芯片的EN、SS/TR、PWRGD等功能引脚来实现上电时序功能(TPS54620芯片的Datasheet上有相应的时序控制原理图)。

如果不用类似于FPGA的控制芯片,那么在设计完上电时序后,断电时序就很难设计。断电时序是否必要?直接断电,是否不妥?

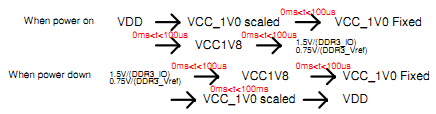

上图是EVM原理图中附带的两个时序要求。后者的时序有办法不用通过控制芯片来实现么?