關於MR腳

- 如果使用這隻接腳來當作觸發RESET控制,WDI接腳的處置是否為浮接。

- 如果輸出一個LOW訊號到MR腳,此時RESET輸出為LOW,如果在這個時候,MR忽然迅速變更為HIGH或是浮接。 這樣會不會影響或是干擾到RESET的輸出狀態,讓原本應該要RESET LOW一段時間忽然變更為HIGH或是不穩定。

關於WDI腳

- 如果使用這隻接腳來當作觸發RESET控制,MR接腳的處置是否為PULL HIGH。

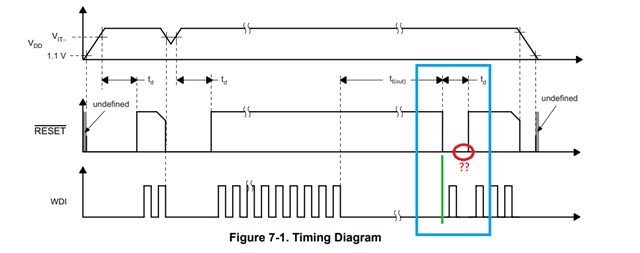

- 當WDI輸入狀態為HGIH或是LOW,而不是HIGH - LOW變化,是否就會觸發RESET動作輸出

- 當RESET被觸發輸出為LOW的同時,我將WDI的輸入,變更為高阻抗,這個時候RESET輸出的狀態是什麼?

會馬上變更為HIGH嗎,還是說RESET的輸出不會受到WDI的輸入狀態影響,會執行RESET輸出LOW一個固定時間。 - 如果不要觸發RESET輸出,WDI需要給它一個頻率變化,這個變化至少是多少頻率,1MHZ是否OK。

共同問題

這顆RESET IC的 RESET 輸出動作,在動作期間,是否會受到MR腳或是WDI腳的狀態影響? 還是說這個FUNCTION,被啟動後,一定會固定執行一段時間後就拉起。

以上請再協助確認。

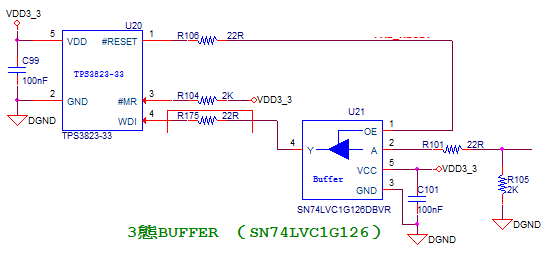

使用WDI和MR的方式,我目前都有使用。

WDI我中間是用一顆三態閘來達成高阻抗狀態,目前看來是沒有問題。 不過還是請協助回覆我上面的疑問。

MR的使用上目前有問題,RESET的啟動時間會被干擾。 我目前是在MR腳和地之間加上一顆電容,讓MR腳不要那麼快被拉起,這顆IC的RESET的動作時間才會比較穩定。 這感覺上是MR是需要一段ACTIVE LOW時間,或是當RESET為LOW時,RESET 輸出狀態還是會受到MR狀態變化的影響,造成RESET應該要持續LOW,可能變成HGIH。