TPS74401的PG引脚表示VOUT的状态,定义中说VOUT超过PG跳变阈值就进入高阻抗状态,VOUT低于PG跳变阈值时PG引脚驱动到一个低阻抗状态,高低阻抗代表了高低数字电平(1、0),那么低阻抗状态的PG就说明了VOUT不正常。(PG引脚需要VBIAS上至少1.1 V的电压才能有一个有效输出。当 VOUT大于(VIT + VHYS)时,PG输出为高阻抗。如果 VOUT低于VIT,或VBIAS低于1.9 V,则漏极开路输出将打开并将PG输出拉低)

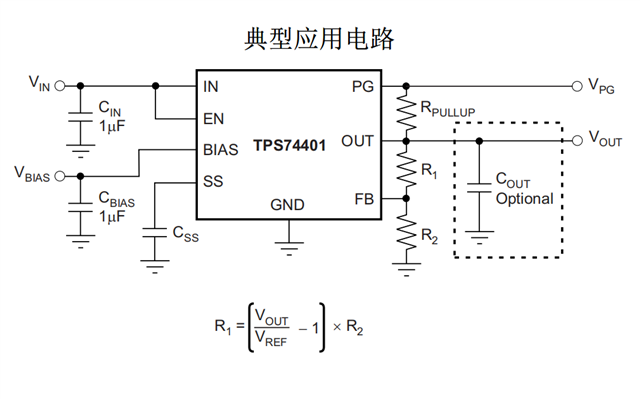

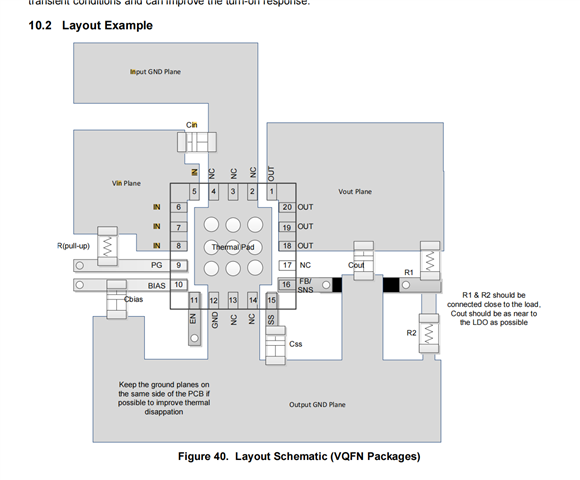

在典型参考电路设计中PG与VOUT间有上拉电阻 ,在Layout布局时,却将PG通过上拉电阻与IN脚相连

,在Layout布局时,却将PG通过上拉电阻与IN脚相连 。描述PG引脚定义时道:”Alternatively, the PG pin can be left floating if output monitoring is not necessary.“但是阅读芯片手册时没有提到PG与IN相连,麻烦大家解答一下~~~

。描述PG引脚定义时道:”Alternatively, the PG pin can be left floating if output monitoring is not necessary.“但是阅读芯片手册时没有提到PG与IN相连,麻烦大家解答一下~~~