Under what circumstances,the two outputs of this chip will be high?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Thank you for contacting TI China E2E forum and choosing our products as part of your solution.

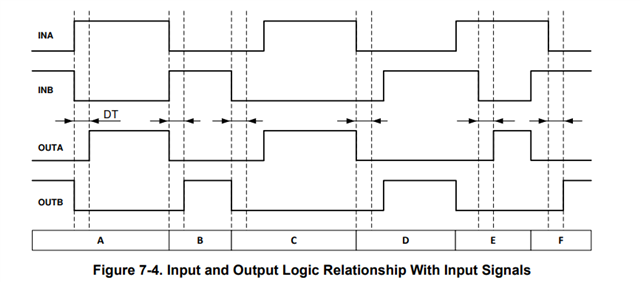

Regarding your query, please check Figure 7-4. Input and Output Logic Relationship With Input Signals in the datasheet.

Page 22 of datasheet.

With deadtime interlock function enabled, instances where both outputs could be high would be induced by external factors.

A common cause for this is dV/dt induced turn-on due to Miller current.

This can happen especially on the low-side MOSFET in a half-bridge configuration, where high dV/dt on the switch node (drain of the low-side MOSFET) can induce a Miller current in the Miller capacitance of the MOSFET (Cgd). This current can bias the gate of the low-side MOSFET and turn it on momentarily.

To avoid this from occurring in a system, we recommend placing a gate-to-source pull down resistor of 10kohms.

Hope this helps.