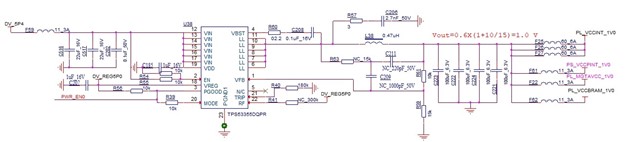

TPS53355的产品设计上遇到以下问题,请帮忙看看设计是否存在问题?有无改善方案?Thanks.

现在使用TPS53355电源芯片给FPGA核电压供电,基本设计要求如下:

输入电压:5.4V;

输出电压:1V;

开关频率:500KHz

负载电压(实测):最大12A

电感型号:470nH,饱和电流18A,内阻4.2mΩ

当前遇到的问题:

FPGA运行过程中,我们测试到输出电压会突然下跌到0.3V,然后再恢复正常。因此想请TI专家帮忙审核电路图是否存在设计错误,电路图截图如下:

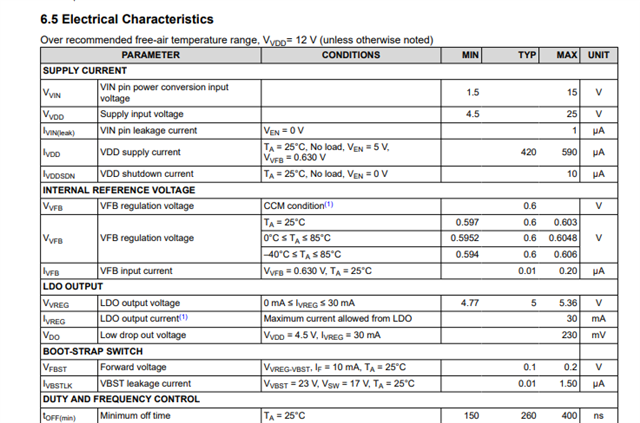

我们使用WEBENCH仿真设计,当输入电压是5.4V时,VDD需要单独供电,请问VDD的输入电压有什么要求?