Hi,Ti

During the debugging of a PCIe device, we encountered an issue where the actual configuration is PCIe Gen3 x2 Lane. The software should display "8GT/s Width x2," but it currently shows "2.5GT/s Width x4." We would like to inquire about the possible conditions that could lead to this discrepancy.

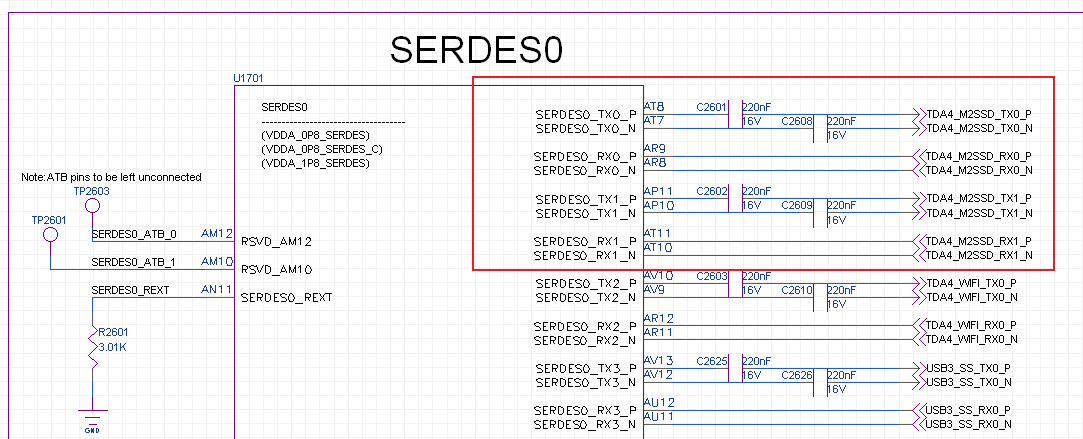

The diagram below shows the SSD schematic configuration

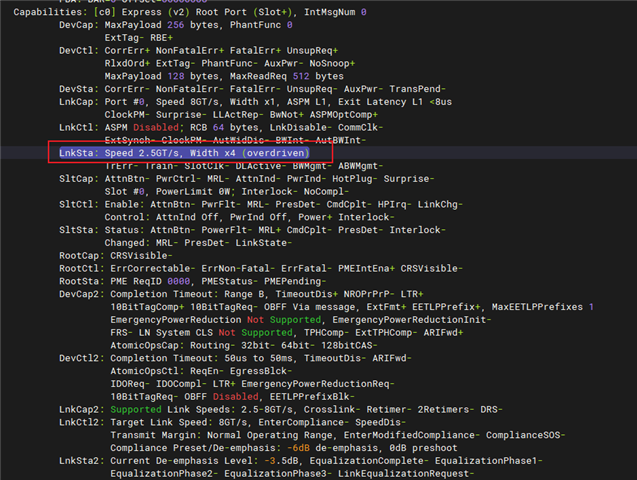

The following figure displays the software log output