Part Number: AM623

The test found that the maximum delay between rx and tx in the same cycle of Ethercat is 200us

Expected to control the maximum delay between rx and tx in the same cycle of Ethercat within 50us

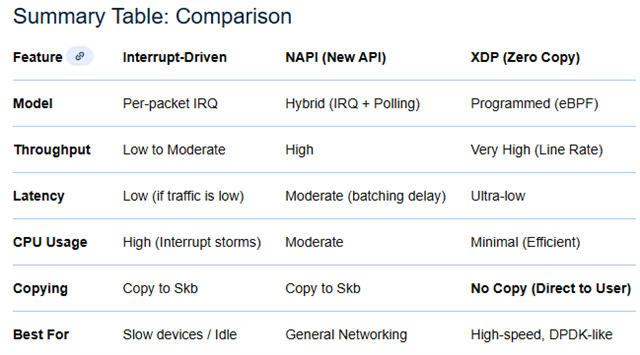

Make modifications in the CPSW driver, and handle Ethercat(0x88A4) and Profinet(0x8892) messages in the interrupt thread.

Ordinary messages use napi framework