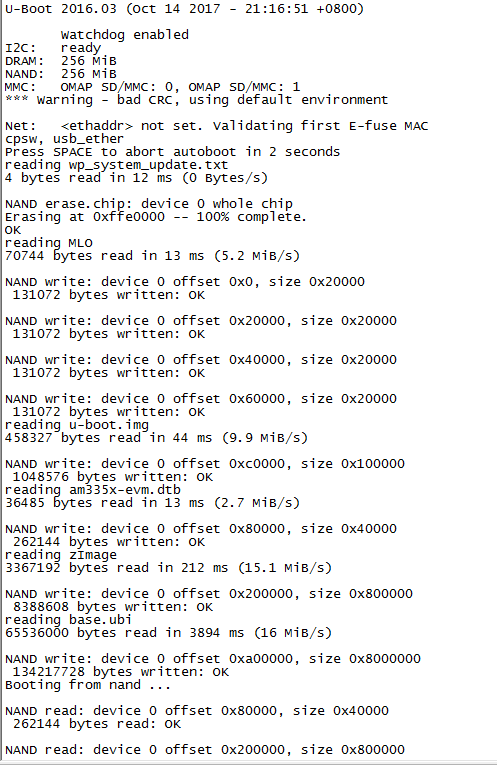

uboot阶段可以正常的对nand进行擦除和读写,如下图

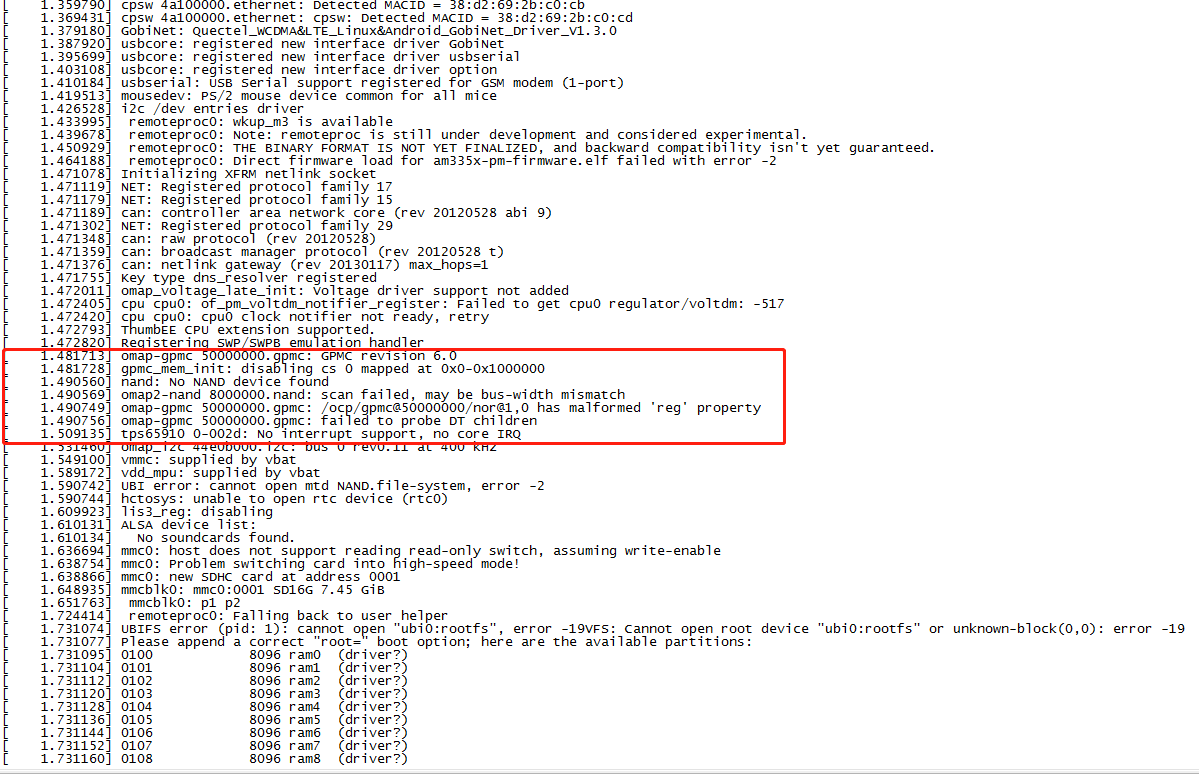

启动kernel之后,在kernel阶段却会出现no nand device,如下图

下图是我的设备树引脚配置和gpmc相关的nand配置

gpmc_pins: pinmux_gpmc_pins {

pinctrl-single,pins = <

0x0 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad0.gpmc_ad0 */

0x4 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad1.gpmc_ad1 */

0x8 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad2.gpmc_ad2 */

0xc (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad3.gpmc_ad3 */

0x10 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad4.gpmc_ad4 */

0x14 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad5.gpmc_ad5 */

0x18 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad6.gpmc_ad6 */

0x1c (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad7.gpmc_ad7 */

0x20 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad8.gpmc_ad8 */

0x24 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad9.gpmc_ad9 */

0x28 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad10.gpmc_ad10 */

0x2c (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad11.gpmc_ad11 */

0x30 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad12.gpmc_ad12 */

0x34 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad13.gpmc_ad13 */

0x38 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad14.gpmc_ad14 */

0x3c (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_ad15.gpmc_ad15 */

0x70 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_wait0.gpmc_wait0 */

0x74 (PIN_INPUT_PULLUP | MUX_MODE0) /* gpmc_wpn.gpmc_wpn */

0x7c (PIN_OUTPUT | MUX_MODE0) /* gpmc_csn0.gpmc_csn0 NAND */

//0x80 (PIN_OUTPUT | MUX_MODE0) /* gpmc_csn1.gpmc_csn1 Ext_IF */

//0x84 (PIN_OUTPUT | MUX_MODE0) /* gpmc_csn2.gpmc_csn2 Ext_IF */

//0x8c (PIN_INPUT_PULLUP | MUX_MODE2) /* gpmc_clk.gpmc_wait1 */

0x90 (PIN_OUTPUT | MUX_MODE0) /* gpmc_advn_ale.gpmc_advn_ale */

0x94 (PIN_OUTPUT | MUX_MODE0) /* gpmc_oen_ren.gpmc_oen_ren */

0x98 (PIN_OUTPUT | MUX_MODE0) /* gpmc_wen.gpmc_wen */

0x9c (PIN_OUTPUT | MUX_MODE0) /* gpmc_be0n_cle.gpmc_be0n_cle */

0xa0 (PIN_OUTPUT | MUX_MODE1) /* lcd_data0.gpmc_a0 */

0xa4 (PIN_OUTPUT | MUX_MODE1) /* lcd_data1.gpmc_a1 */

0xa8 (PIN_OUTPUT | MUX_MODE1) /* lcd_data2.gpmc_a2 */

0xac (PIN_OUTPUT | MUX_MODE1) /* lcd_data3.gpmc_a3 */

0xb0 (PIN_OUTPUT | MUX_MODE1) /* lcd_data4.gpmc_a4 */

0xb4 (PIN_OUTPUT | MUX_MODE1) /* lcd_data5.gpmc_a5 */

0xb8 (PIN_OUTPUT | MUX_MODE1) /* lcd_data6.gpmc_a6 */

0xbc (PIN_OUTPUT | MUX_MODE1) /* lcd_data7.gpmc_a7 */

0xc0 (PIN_OUTPUT | MUX_MODE1) /* lcd_data8.gpmc_a12 */

0xc4 (PIN_OUTPUT | MUX_MODE1) /* lcd_data9.gpmc_a13 */

0xc8 (PIN_OUTPUT | MUX_MODE1) /* lcd_data10.gpmc_a14 */

0xcc (PIN_OUTPUT | MUX_MODE1) /* lcd_data11.gpmc_a15 */

0xd0 (PIN_OUTPUT | MUX_MODE1) /* lcd_data12.gpmc_a16 */

0xd4 (PIN_OUTPUT | MUX_MODE1) /* lcd_data13.gpmc_a17 */

0xd8 (PIN_OUTPUT | MUX_MODE1) /* lcd_data14.gpmc_a18 */

0xdc (PIN_OUTPUT | MUX_MODE1) /* lcd_data15.gpmc_a19 */

0xe0 (PIN_OUTPUT | MUX_MODE1) /* lcd_vsync.gpmc_a8 */

0xe4 (PIN_OUTPUT | MUX_MODE1) /* lcd_hsync.gpmc_a9 */

0xe8 (PIN_OUTPUT | MUX_MODE1) /* lcd_pclk.gpmc_a10 */

0xec (PIN_OUTPUT | MUX_MODE1) /* lcd_ac_bias_en.gpmc_a11 */

>;

};

&gpmc {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&gpmc_pins>;

ranges = <0 0 0x08000000 0x1000000 /* CS0: 16MB for NAND */

//1 0 0x10000000 0x1000000 /* CS1: 16MB for EXT-IF1 */

// 2 0 0x11000000 0x1000000 /* CS2: 16MB for EXT-IF2 */

>;

nand@0,0 {

compatible = "ti,omap2-nand";

reg = <0 0 4>; /* CS0, offset 0, IO size 4 */

interrupt-parent = <&gpmc>;

interrupts = <0 IRQ_TYPE_NONE>, /* fifoevent */

<1 IRQ_TYPE_NONE>; /* termcount */

rb-gpios = <&gpmc 0 GPIO_ACTIVE_HIGH>; /* gpmc_wait0 */

ti,nand-xfer-type = "prefetch-dma";

ti,nand-ecc-opt = "bch8";

ti,elm-id = <&elm>;

nand-bus-width = <8>;

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <44>;

gpmc,cs-wr-off-ns = <44>;

gpmc,adv-on-ns = <6>;

gpmc,adv-rd-off-ns = <34>;

gpmc,adv-wr-off-ns = <44>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <40>;

gpmc,oe-on-ns = <0>;

gpmc,oe-off-ns = <54>;

gpmc,access-ns = <64>;

gpmc,rd-cycle-ns = <82>;

gpmc,wr-cycle-ns = <82>;

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

/* MTD partition table */

/* All SPL-* partitions are sized to minimal length

* which can be independently programmable. For

* NAND flash this is equal to size of erase-block */

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "NAND.SPL";

reg = <0x00000000 0x000020000>;

};

partition@1 {

label = "NAND.SPL.backup1";

reg = <0x00020000 0x00020000>;

};

partition@2 {

label = "NAND.SPL.backup2";

reg = <0x00040000 0x00020000>;

};

partition@3 {

label = "NAND.SPL.backup3";

reg = <0x00060000 0x00020000>;

};

partition@4 {

label = "NAND.u-boot-spl-os";

reg = <0x00080000 0x00040000>;

};

partition@5 {

label = "NAND.u-boot";

reg = <0x000C0000 0x00100000>;

};

partition@6 {

label = "NAND.u-boot-env";

reg = <0x001C0000 0x00020000>;

};

partition@7 {

label = "NAND.u-boot-env.backup1";

reg = <0x001E0000 0x00020000>;

};

partition@8 {

label = "NAND.kernel";

reg = <0x00200000 0x00800000>;

};

partition@9 {

label = "NAND.file-system";

reg = <0x00A00000 0x0F600000>;

};

};