Other Parts Discussed in Thread: AM5728,

手头有块创龙的TL5728板子,经调试修改ARM A15的CMD文件,使其可以在DDR0中运行代码,主程序中已调用了Cache初始化程序,在DDR0中运行代码发现比在 OCMC_RAM1段中运行快很多,AM5728的CMD配置如下:

--retain="*(.intvecs)"

-c

-stack 0x800

-heap 0x2000

--args 0x1000

-e Entry

#define A

//#define B

//#define C

MEMORY

{

VECTORS : o = 0x40300000, l = 0x00002000 /* 中断向量表,占用512字节空间 */

OCMC_RAM1 : o = 0x40302000, l = 0x0007E000 /* 512kB L3 OCMC RAM1 */

//OCMC_RAM1 : o = 0x40300000, l = 0x00080000 /* 512kB L3 OCMC RAM1 */

//VECTORS : o = 0x40400000, l = 0x00002000 /* 中断向量表,占用512字节空间 */

//OCMC_RAM2 : o = 0x40402000, l = 0x000FE000 /* 1MB L3 OCMC RAM2 */

OCMC_RAM2 : o = 0x40400000, l = 0x00100000 /* 1MB L3 OCMC RAM2 */

OCMC_RAM3 : o = 0x40500000, l = 0x00100000 /* 1MB L3 OCMC RAM3 */

VECTOR : o = 0x80000000, l = 0x00002000 /* 中断向量表,占用512字节空间 */

DDR0 : o = 0x80002000, l = 0x3FFFE000 /* 1GB external DDR Bank 0 */

DDR1 : o = 0xC0000000, l = 0x40000000 /* 1GB external DDR Bank 1 */

}

SECTIONS

{

.intvecs > VECTORS

.text > DDR0//OCMC_RAM1

.stack > DDR0//OCMC_RAM1

.bss > OCMC_RAM1

.cio > OCMC_RAM1

.const > OCMC_RAM1

.data > DDR0//OCMC_RAM1

.switch > OCMC_RAM1

.sysmem > OCMC_RAM1

.far > OCMC_RAM1

.args > OCMC_RAM1

.ppinfo > OCMC_RAM1

.ppdata > OCMC_RAM1

RUN_START(bss_start)

RUN_END(bss_end)

/* COFF sections */

.pinit > OCMC_RAM1

.cinit > OCMC_RAM1

/* EABI sections */

.binit > OCMC_RAM1

.init_array > OCMC_RAM1

.neardata > OCMC_RAM1

.fardata > OCMC_RAM1

.rodata > OCMC_RAM1

}

以上对CMD文件的修改,还可以让堆栈和已初始化变量也分配到DDR0中

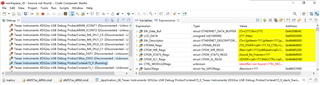

对照上述修改,将BeagleBone AI的 ARM A15测试工程的CMD文件做完全相同的修改,发现程序无法运行,刚把out文件加载到core0中还未点击运行,程序就跑飞,如下

对CMD文件的段分配作如下修改:

.text > OCMC_RAM1

.stack > OCMC_RAM1

.data > DDR0

再次编译,链接目标,程序运行正常,已初始化的变量也能正常分配到DDR0中,在变量观察窗口能看到相应的变量都是正确的,就这说明DDR存储器在GEL文件中是已被正确配置和初始化了的,否则变量就无法正确分配到DDR0中了。但程序却无法加载到DDR0中,这样的话代码运行速度将大大降低

由此有以下几个疑问:

1 系统的内部RAM运行代码的速度怎么比外部的DDR0要慢很多呢?代码中我已调用了Cache使能的函数,应该是对内部和外部的RAM都做了Cache使能吧

2 经上述测试,显然DDR存储器在GEL文件中是正确配置了的,那为啥AM5729中不能在DDR中运行代码,而AM5728却可以,是否还要做什么配置?或者这个问题是不是属于BeagleBone AI的一个特有的硬件问题,因为我手头的这个BeagleBone AI是第一个硬件版本的,之前我在另一个帖子中提到过这个第一版的一个硬件问题,所以我在想这是不是另一个硬件问题。

希望TI工程师帮我解决这个DDR不能运行代码的问题,谢谢