调了几天还是不知道是啥问题导致这样的?所以想请教一下!谢谢!

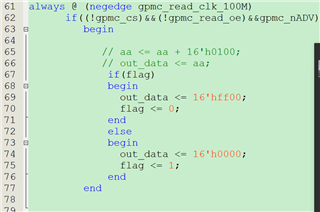

FPGA发aa递增数据,GPMC读取正确。但是发ff00和0000循环发,GPMC读取就不正确,很奇怪!是不是我GPMC时序配置不对?

GPMC_CONFIG2_1 0x00001F00;

GPMC_CONFIG3_1 0x00000200;

GPMC_CONFIG4_1 0x00001F0E;

GPMC_CONFIG5_1 0x010F001F;

GPMC_CONFIG6_1 0x00000000;

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,

建议你先不用EDMA,用cpu直接读取数据,排除EDMA配置的问题。

clk的极性FPGA和GPMC是否有正确匹配?

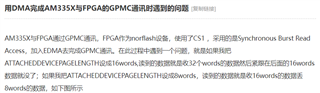

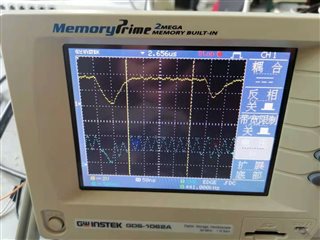

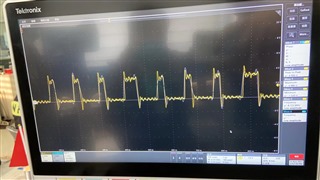

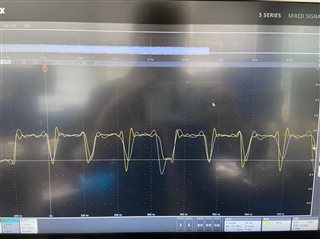

我连上FPGA用示波器看了下信号,如下,图一是25M时钟(100M四分频,示波器最大只能测到60M频率信号)和nAVD信号,图二是时钟25M时钟(100M四分频)和OE信号,如下:

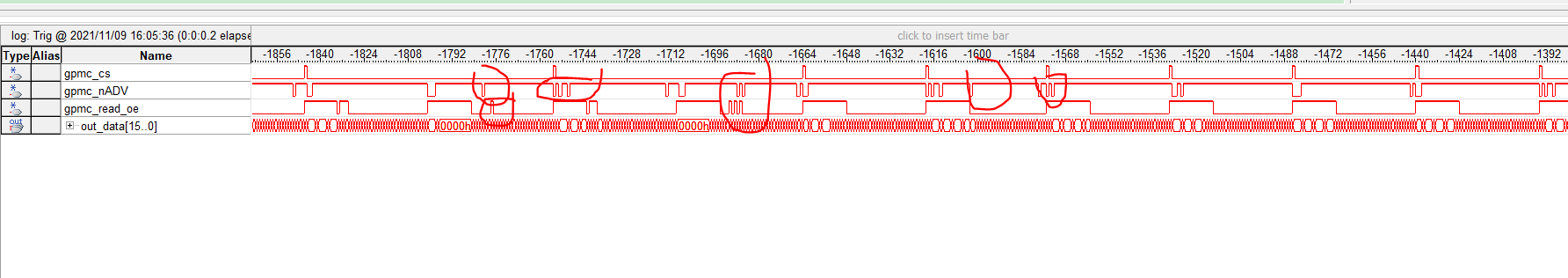

发现示波器没有这种干扰脉冲,用FPGA SignalTap捕捉CS nAVD OE时序波形,发00ff 0000依次这样发,发现有干扰脉冲(如下图),示波器没有,就怀疑可能是SignalTap捕捉bug。

现在的现象就是很奇怪,递增发数据,比如1 2 3 4 5 。。。或者2 4 6 8 10。。。,1 3 4 6 7 9.。。。这样,GPMC数据读取都是正确的, FPGA SignalTap捕捉CS nAVD OE时序波形,都没有脉冲干扰,示波器看也没有。但是数据变化比较大的发,比如 0000 ffff 0000 ffff 。。。这样,就会出现GPMC读取有的是e000 ff80 等会出现这样一些错误的数据,FPGA SignalTap捕捉CS nAVD OE时序波形会看到有脉冲干扰,但是示波器看没有(不知道是不是示波器测量频率有限捕捉不到),如果示波器捕捉的时序是正确的的,FPGA SignalTap捕捉有bug,那我就怀疑是我的程序时序配置有问题,导致数据变化大的发会出错。但是很奇怪,为什么变化不大的数发,就不会有错误,变化大的发,就会出现数据读取错误,麻烦能不能看下我时序配置,是不是我哪里没配置好!谢谢!

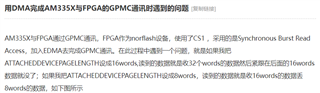

#define GPMC_CONFIG1_i 0x60801200 // burst,sync,8words,16bit,NOR FLASH like,Address and data multiplexed,100M

#define GPMC_CONFIG2_i 0x00000500 // CSRDOFFTIME=5cy CSONTIME =0cy

#define GPMC_CONFIG3_i 0x00000200 // ADVRDOFFTIME = 2cy ADVONTIME=0 That ADV TIME no used is to read datas without address.

#define GPMC_CONFIG4_i 0x00000503 // OEOFFTIME=5cy OEEXTRADELAY OEONTIME=3cy PAGEBURSTACCESSTIME = 1cy(if 0 slow speed)

#define GPMC_CONFIG5_i 0x01040005 // PAGEBURSTACCESSTIME = 1cy(if 0 slow speed) RDACCESSTIME=4cy RDCYCLETIME=5cy

#define GPMC_CONFIG6_i 0x00000000 //CYCLE2CYCLEDELAY=0cy

#define GPMC_CONFIG7_i 0x00000F42 // set up CONFIG7 and enable cs3,16M, baseAdd 0x02

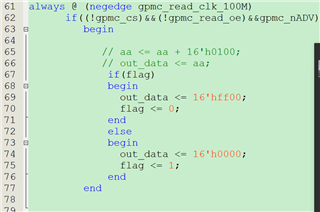

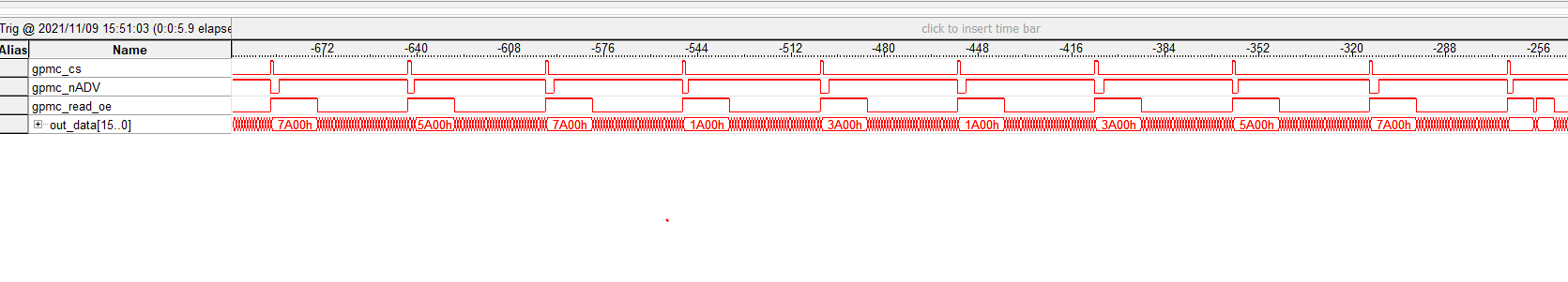

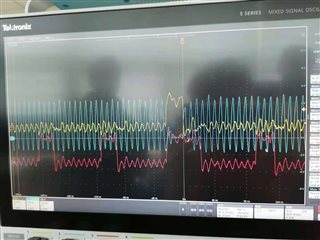

下图是配置后,递增发数据FPGA SignalTap捕捉到的,上图是发FF00 0000 ff00 0000捕捉到的。

你好,

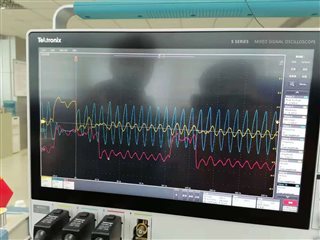

我们用高频示波器查看信号,不连FPGA看GPMC输出时序和连FPGA看GPMC输出时序,如下:

上图是OE信号,黄线是没有连FPGA,蓝线是连FPGA

上图是nAVD信号,黄线是不连FPGA的,另一种颜色线是连FPGA的

好像信号没有受到FPGA干扰,可能应该是程序时序配置问题,或者其他没想到的错误原因。但是程序时序问题,为啥会出现FPGA发的数据数据值前后变化不大,比如递增加一或加二发,GPMC读取正确。数据前后变化大了就读取不对,比如0000 ffff?这可能是啥原因呢?从来没遇到过

你好,

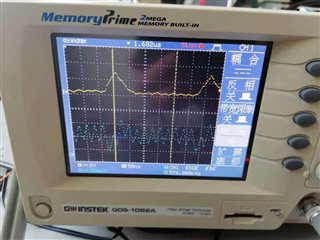

我用高频示波器仔细捕捉了下没有接FPGA的时序波形,如下:

蓝线是100M时钟,黄线是片选cs,红线是OE读使能(低电平效),和时序配置好像一样(如下)。我想问下GPMC数据线上是GPMC时钟低电平改变数据,高电平读数据吗?谢谢!

#define GPMC_CONFIG1_i 0x60801200 // burst,sync,8words,16bit,NOR FLASH like,Address and data multiplexed,100M

#define GPMC_CONFIG2_i 0x00000500 // CSRDOFFTIME=5cy CSONTIME =0cy

#define GPMC_CONFIG3_i 0x00000200 // ADVRDOFFTIME = 2cy ADVONTIME=0 That ADV TIME no used is to read datas without address.

#define GPMC_CONFIG4_i 0x00000503 // OEOFFTIME=5cy OEEXTRADELAY OEONTIME=3cy PAGEBURSTACCESSTIME = 1cy(if 0 slow speed)

#define GPMC_CONFIG5_i 0x01040005 // PAGEBURSTACCESSTIME = 1cy(if 0 slow speed) RDACCESSTIME=4cy RDCYCLETIME=5cy

#define GPMC_CONFIG6_i 0x00000000 //CYCLE2CYCLEDELAY=0cy

#define GPMC_CONFIG7_i 0x00000F42 // set up CONFIG7 and enable cs3,16M, baseAdd 0x02

你好,

RDACCESSTIME的解释是Delay between start cycle time and first data valid。这个信号和OE没有直接关系,你的FPGA应该参考这个信号来提供数据。