TI的工程师,您好!

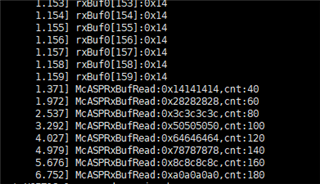

我通过AM5718的DSP核操作MCASP EDMA传输的时候,将输出引脚与输入引脚进行短接,可以实现连续地输出波形,在传输过程中也能够对发送的数据进行修改并能在波形上体现出来,但rxBuf只能接收到第一次传输的数据,之后就无法接收到数据了,也就是说当我把rxBuf清空之后里面的数据将会一直为0不再更新,而在此过程中是一直有输出波形的,并且接收寄存器MCASP_RXBUF的值不为0。

我的猜测:

1、接收寄存器MCASP_RXBUF是能够接收到数据的,但是无法再次通过EDMA传输至rxBuf(但是EDMA RX回调函数一直能够进入,说明是一直在进行EDMA接收传输的,那么原因可能就是传输的源地址或者目标地址不对了)。

2、txBuf能够通过EDMA将数据传输至发送寄存器MCASP_TXBUF并发送出去。

参考例程:\processor_sdk_rtos_am57xx_06_03_02_08\pdk_am57xx_1_0_18\packages\ti\board\diag\mcasp_audiodc\ ,仅对输出输入引脚做了修改。

测试程序如下:

/cfs-file/__key/communityserver-discussions-components-files/120/mcasp_5F00_audiodc_5F00_test.c

/cfs-file/__key/communityserver-discussions-components-files/120/mcasp_5F00_audiodc_5F00_test.h

参考了以下e2e帖子:

问题:我在实现MCASP EDMA连续接收数据并传输至rxBuf还缺少了些什么配置或者有哪些配置有错误?

期待您的解答,谢谢!