Part Number: TMS320C6727B

用示波器观察到如图所示的波形。其中蓝色为flash器件的时钟,即EM_CLK,频率为55MHz。黄色为CE信号,绿色为WE信号。为什么在CE信号为低电平

的时间段内,WE信号会出现一次高电平的变化呢?正常WE应该是一直保持低电平。是我的时序寄存器配置的有问题吗,还是其他原因

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320C6727B

用示波器观察到如图所示的波形。其中蓝色为flash器件的时钟,即EM_CLK,频率为55MHz。黄色为CE信号,绿色为WE信号。为什么在CE信号为低电平

的时间段内,WE信号会出现一次高电平的变化呢?正常WE应该是一直保持低电平。是我的时序寄存器配置的有问题吗,还是其他原因

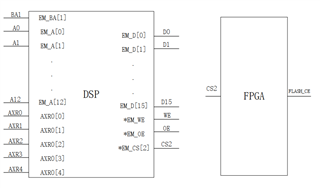

如图所示。黄色为WE信号,蓝色为BA1信号,绿色为BA0信号。其余地址线与数据线上的时序都完全正常。

按照上面代码中的DSP地址,BA1应为高电平,BA0为低电平。但BA1的波形出现了低电平。

我又将代码中的DSP地址进行修改,将DSP地址改为0x9000AAAB,此时的BA1与BA0均应为高电平。但示波器显示波形还是如图所示,即没有变化。

将DSP地址改为0x9000AAAC,此时的BA1与BA0均应为低电平。但示波器显示波形还是如图所示,即没有变化。

想问下这是哪里出现了问题呢?

谢谢您。还想请您帮个忙,这个帖子有几处修改一下。

①代码中的注释翻译成英文

②But he found the WE is toggled twice in one write cycle and the BA0 is not correct. Please see below snapshot.

这句话改成:

But he found the WE is toggled twice in one write cycle and the BA0 and BA1 are not correct. Please see below snapshot.

③在最后加上一句话:由于DSP使用的是BGA封装,所以没办法直接使用示波器测量引脚电平。我将DSP上的相关引脚连接到了FPGA上,通过FPGA的引脚使用示波器查看波形。

万分感谢。

此外,如果可以的话,希望能够将下面的问题也一并放入同一个英文帖子中。

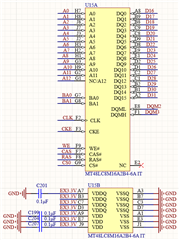

为了检验BA1与BA0是否有问题,我又使用SDRAM做了实验。电路图如图所示。所使用的型号为MT48LC8M16A2B4。同样也通过FPGA连接示波器查看波形。

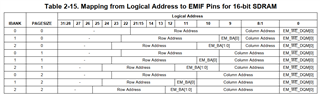

根据“TMS320C672x DSP EMIF User's Guide”(编号SPRU711C)中的Table 2-8,结合使用的SDRAM型号可得:IBANK=2,PAGESIZE=1。

再根据SPRU711C中的Table 2-15,也即第二个图中的第6行,可知:BA[1:0]为逻辑地址的第10和11位。使用示波器测量发现:无论怎么修改地址,BA1和BA0均始终为高电平。请问出现这个问题的原因是什么?实验的主要代码如下:

while(1)

{

*(unsigned int *)0x8000AAAA=0x1234;

Delay(20);

}

关于逻辑地址,我的理解是,比如TMS320C6727B型号的DSP分配给SDRAM的地址为0x80000000-0x8FFFFFFF。这个地址就是逻辑地址。也就是说,代码中的地址0x8000AAAA,对应的BA[1]=1,BA[0]=0。

如果我的理解是正确的,那么上面的实验结果就是正确的。如果我的理解错误,那么希望得到关于逻辑地址的正确解释,然后我重新做SDRAM实验。谢谢。

请看下面工程师的回复。请问Flash_5555h这个变量是怎么定义的?是8bit还是16bit的?

it appears to be working in 8bit mode. Can you read out the register value for A1CR (not just what is configured in code)? It may not be getting written correctly.

Also, how is variable Flash_5555h declared? Is it defined as a byte (8bit) or word (16bit) element?

我注意到工程师的回复:

Can you show the processor side of the schematic connection? Are you showing signal EM_WE or EM_WE_DQM in the scope shot?

下面是我的回复:

(1)处理器端的连接如图所示。FLASH的片选信号FLASH_CE是在FPGA端,通过下面VHDL程序将FLASH_CE与CS2连接起来,并已将程序烧进FPGA芯片中。

(1)处理器端的连接如图所示。FLASH的片选信号FLASH_CE是在FPGA端,通过下面VHDL程序将FLASH_CE与CS2连接起来,并已将程序烧进FPGA芯片中。

CS_2 <= FLASH_CE;

此外,由于DSP采用BGA封装,所以无法直接使用示波器测量引脚电平。我将DSP上的相关引脚通过编写VHDL程序连接到了FPGA上,通过FPGA的引脚使用示波器查看波形。

(2)示波器显示的是EM_WE信号。

辛苦您帮我回复给工程师,万分感谢。

您好,下面是工程师的回复:

I'm not sure what is going on here. Does the write complete successfully? Does the same behavior happen on a read?

下面是我的回复:

①写操作没有成功

②由于SST39VF800A读操作时也需要向固定地址写入数据,由于无法写入数据,所以也无法进行读操作。读数据时执行一次写操作与写数据执行一次写操作的波形是一样的。

麻烦您回复给工程师,辛苦啦。

请看下面工程师的回复。

is it possible that your compiler is expecting the *(unsigned int *) to be a pointer to a 32-bit value? So when you perform the write, it is actually performing 2 16-bit writes. That seems to be what the waveforms are indicating. Can you try declaring the variable as an (*unsigned short *) ? You may need to inspect the assembly code produced by the complier to ensure it is performing the correct amount of writes.