Hi Sir:

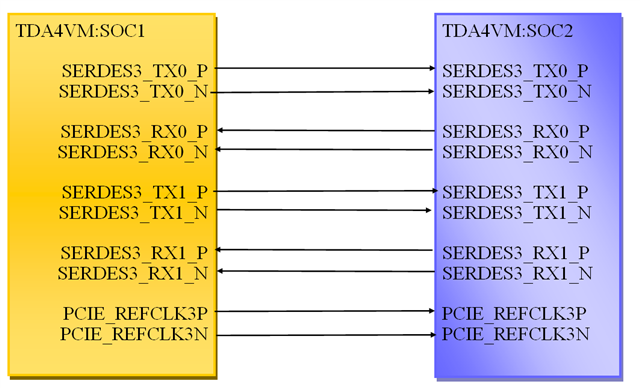

My costromer board is two TDA4VM SOC, and soc1 is pcie3 rc , soc2 is pcie3 ep.

linux SDK is 8.04.

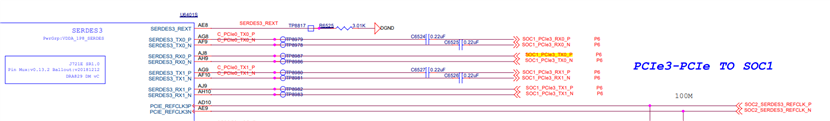

And the Hardware SCH is this

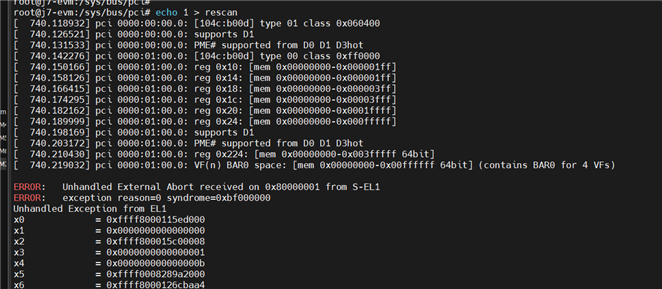

When soc1 and soc2 power on, soc1 lspci can see 0x104c:b00d soc2 bridge device, and soc1 echo 1 > /sys/bus/pci/devices/0000:00:00.0/remove , echo 1 > /sys/bus/pci/rescan ok.

But the problem is : After i creat Endpot function in soc2 (ep devcie) , and then in soc1(rc) echo 1 > /sys/bus/pci/devices/0000:00:00.0/remove , echo 1 > /sys/bus/pci/rescan, the soc1 system crash immediately.

log is this:

..... My Operating Steps:

soc2:

cd /sys/kernel/config/pci_ep

mkdir functions/pci_epf_test/func1

echo 0x104c > functions/pci_epf_test/func1/vendorid

echo 0xb00d > functions/pci_epf_test/func1/deviceid

echo 12 > functions/pci_epf_test/func1/msi_interrupts

echo 12 > functions/pci_epf_test/func1/msix_interrupts

ln -s functions/pci_epf_test/func1 controllers/2930000.pcie-ep

echo 1 > controllers/2930000.pcie-ep/start

soc1:

echo 1 > /sys/bus/pci/devices/0000:00:00.0/remove

echo 1 > /sys/bus/pci/rescan

Dts setting:

soc1:

&pcie3_rc {

/*reset-gpios = <&exp2 20 GPIO_ACTIVE_HIGH>;*/

phys = <&serdes3_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <2>;

};

&serdes3 {

assigned-clocks = <&serdes3 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz3_pll1_refclk>;

serdes3_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz3 1>, <&serdes_wiz3 2>;

};

};

soc2:

&pcie3_ep {

/delete-property/ power-domains;

phys = <&serdes3_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <2>;

};

&serdes3 {

assigned-clocks = <&serdes3 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz3_pll1_refclk>;

serdes3_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz3 1>, <&serdes_wiz3 2>;

};

};

...............................

So, what reason can is? like refclk setting ? etc...

How can I do ......