Part Number: TDA4VH-Q1

tda4vh sdk8.6平台中

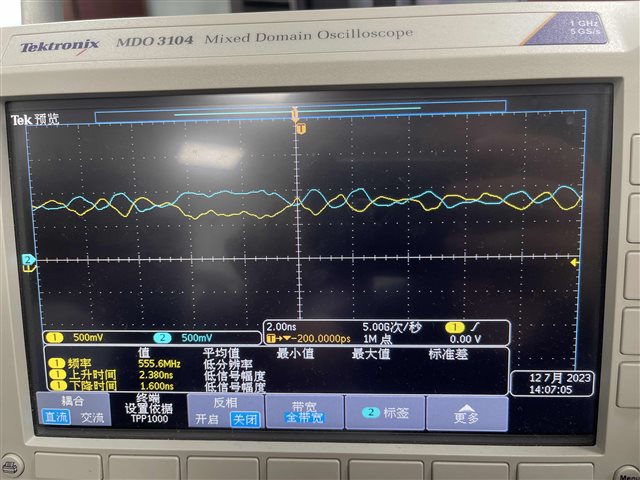

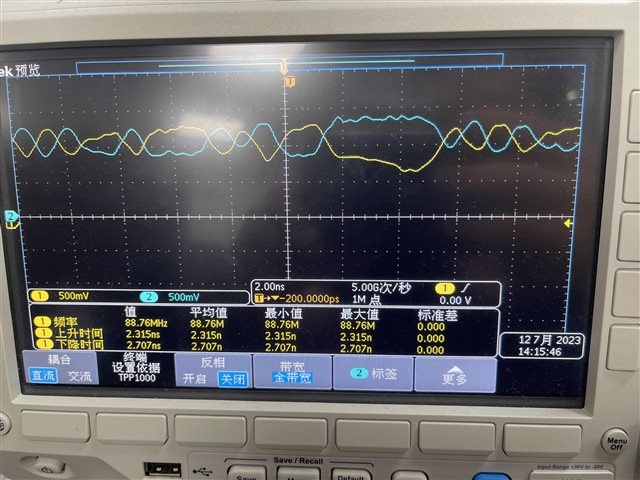

rtos中调试2-0的sgmii phy

需要配置sgmii与serdes

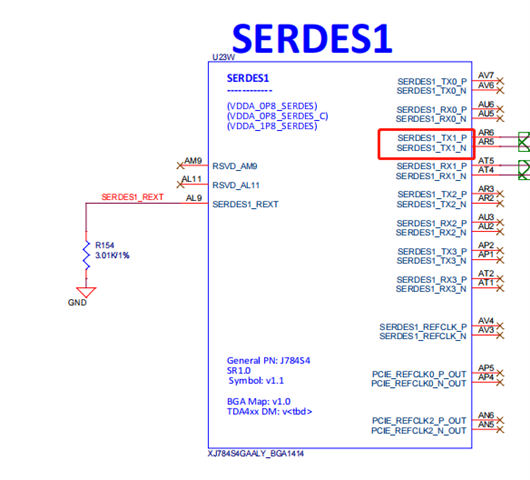

serdes1 lane 1

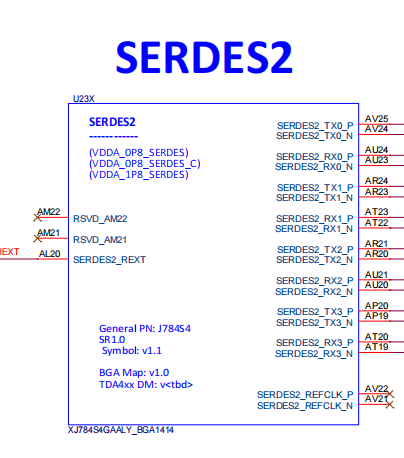

serdes 2 lane 0 1 2 3 4

过程中出现pll错误

CpswMacPort_setSgmiiInterface: MAC 4: SERDES PLL is not locked

[MCU2_0] 17.794998 s: EnetMcm: CPSW_9G on MAIN NAVSS [MCU2_0] 17.810964 s: PHY 0 is no alive [MCU2_0] 17.811022 s: PHY 1 is no alive [MCU2_0] 17.811053 s: PHY 2 is alive [MCU2_0] 17.811080 s: PHY 3 is no alive [MCU2_0] 17.811107 s: PHY 4 is no alive [MCU2_0] 17.811135 s: PHY 5 is no alive [MCU2_0] 17.811161 s: PHY 6 is no alive [MCU2_0] 17.811187 s: PHY 7 is no alive [MCU2_0] 17.811214 s: PHY 8 is no alive [MCU2_0] 17.811241 s: PHY 9 is no alive [MCU2_0] 17.811267 s: PHY 10 is no alive [MCU2_0] 17.811295 s: PHY 11 is no alive [MCU2_0] 17.811323 s: PHY 12 is no alive [MCU2_0] 17.811350 s: PHY 13 is no alive [MCU2_0] 17.811377 s: PHY 14 is no alive [MCU2_0] 17.811404 s: PHY 15 is no alive [MCU2_0] 17.811432 s: PHY 16 is no alive [MCU2_0] 17.811459 s: PHY 17 is no alive [MCU2_0] 17.811486 s: PHY 18 is no alive [MCU2_0] 17.811513 s: PHY 19 is no alive [MCU2_0] 17.811547 s: PHY 20 is no alive [MCU2_0] 17.811575 s: PHY 21 is no alive [MCU2_0] 17.811601 s: PHY 22 is no alive [MCU2_0] 17.811627 s: PHY 23 is no alive [MCU2_0] 17.811654 s: PHY 24 is no alive [MCU2_0] 17.811681 s: PHY 25 is no alive [MCU2_0] 17.811707 s: PHY 26 is no alive [MCU2_0] 17.811734 s: PHY 27 is no alive [MCU2_0] 17.811760 s: PHY 28 is no alive [MCU2_0] 17.811787 s: PHY 29 is no alive [MCU2_0] 17.811813 s: PHY 30 is no alive [MCU2_0] 17.811846 s: EnetMcm_enablePorts() +to open MAC port: 3 [MCU2_0] 17.812042 s: CpswMacPort_setSgmiiInterface: MAC 4: SERDES PLL is not locked 0x0 [MCU2_0] 17.812078 s: CpswMacPort_setSgmiiInterface: [MCU2_0] 17.812113 s: Assertion @ Line: 2201 in src/mod/cpsw_macport.c: false

{

/* Configure SerDes clocks */

EthFwBoard_configTorrentClks();

/* Configure SerDes for QSGMII functionality */

boardStatus = Board_serdesCfgSgmii();

EnetAppUtils_assert(boardStatus == BOARD_SOK);

boardStatus = Board_serdesCfgSgmii_serdes1();

// EnetAppUtils_assert(boardStatus == BOARD_SOK);

Board_STATUS Board_CfgSgmii_serdes1(void)

{

CSL_SerdesResult result;

CSL_SerdesLaneEnableStatus laneRetVal = CSL_SERDES_LANE_ENABLE_NO_ERR;

CSL_SerdesLaneEnableParams serdesLane0EnableParams = {0};

printf("%s %d \n",__func__,__LINE__);

memset(&serdesLane0EnableParams, 0, sizeof(serdesLane0EnableParams));

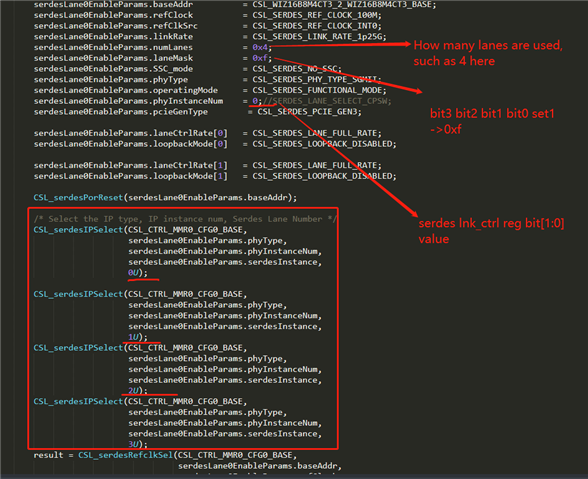

/* SGMII Config */

serdesLane0EnableParams.serdesInstance = (CSL_SerdesInstance)CSL_TORRENT_SERDES1;

serdesLane0EnableParams.baseAddr = CSL_WIZ16B8M4CT3_1_WIZ16B8M4CT3_BASE;

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_100M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT1;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G;

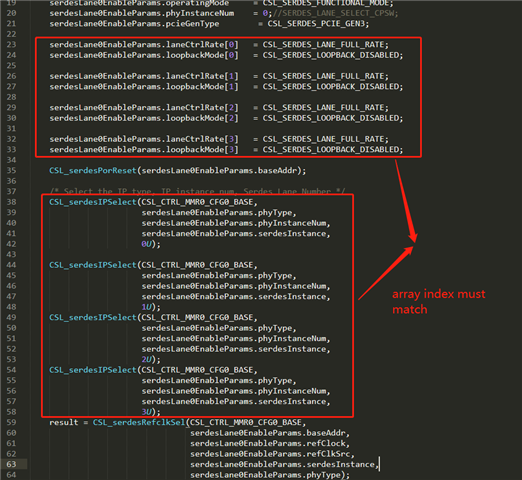

serdesLane0EnableParams.numLanes = 0x2;

serdesLane0EnableParams.laneMask = 0x4;

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

serdesLane0EnableParams.phyInstanceNum = BOARD_SERDES_LANE_SELECT_CPSW;

serdesLane0EnableParams.pcieGenType = CSL_SERDES_PCIE_GEN3;

serdesLane0EnableParams.laneCtrlRate[0] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[0] = CSL_SERDES_LOOPBACK_DISABLED;

serdesLane0EnableParams.laneCtrlRate[1] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[1] = CSL_SERDES_LOOPBACK_DISABLED;

CSL_serdesPorReset(serdesLane0EnableParams.baseAddr);

/* Select the IP type, IP instance num, Serdes Lane Number */

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

1U);

result = CSL_serdesRefclkSel(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.baseAddr,

serdesLane0EnableParams.refClock,

serdesLane0EnableParams.refClkSrc,

serdesLane0EnableParams.serdesInstance,

serdesLane0EnableParams.phyType);

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

/* Assert PHY reset and disable all lanes */

CSL_serdesDisablePllAndLanes(serdesLane0EnableParams.baseAddr, serdesLane0EnableParams.numLanes, serdesLane0EnableParams.laneMask);

/* Load the Serdes Config File */

result = CSL_serdesEthernetInit(&serdesLane0EnableParams);

/* Return error if input params are invalid */

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

/* Common Lane Enable API for lane enable, pll enable etc */

laneRetVal = CSL_serdesLaneEnable(&serdesLane0EnableParams);

if (laneRetVal != 0)

{

return BOARD_FAIL;

}

return BOARD_SOK;

}

从打印看,好像2-0卡死了

Board_ethConfigCpsw9g 663 [MCU2_0] 61.678121 s: Board_CfgSgmii_serdes1 393 [MCU2_1] 47.263577 s: CIO: Init ... Done !!! [MCU2_1] 47.263628 s: ### CPU Frequency = 1000000000 Hz [MCU2_1] 47.263661 s: CPU is running FreeRTOS [MCU2_1] 47.263681 s: APP: Init ... !!! [MCU2_1] 47.263700 s: SCICLIENT: Init ... !!! [MCU2_1] 47.263865 s: SCICLIENT: DMSC FW version [8.6.3--v08.06.03 (Chill Capybar] [MCU2_1] 47.263899 s: SCICLIENT: DMSC FW revision 0x8

请问一下,如何配置原理图中所需要的sgmii 及serdes并确保及正常工作