Part Number: TMS320C6748

Other Parts Discussed in Thread: TXS0102

你好:

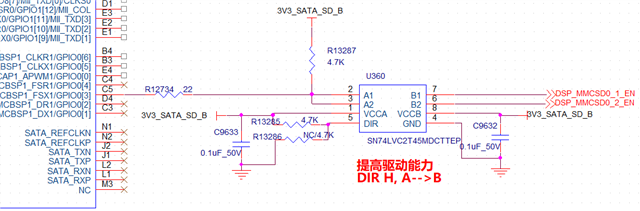

有一个项目用到C6748和TI的SN74LVC2T45MDCTTEP的芯片,如下是原理图,想用C6748的GPIO控制SN74LVC2T45MDCTTEP这个芯片,如果C6748和SN74LVC2T45MDCTTEP正常供电,C6748的GPIO能正常的控制SN74LVC2T45MDCTTEP的A1,A2脚的高低,但是我现在有一个应用场景,如下:

不给C6748供电,但是SN74LVC2T45MDCTTEP正常供电,并且SN74LVC2T45MDCTTEP的A1,A2脚上拉到3.3V,SN74LVC2T45MDCTTEP的B1,B2脚始终为低,是不是因为C6748的GPIO口有很大的下拉电阻的原因?还是由于不给C6748供电的原因,所有的GPIO口会强制拉低的原因,所以SN74LVC2T45MDCTTEP的A1,A2脚会被强制拉低,从而SN74LVC2T45MDCTTEP的B1,B2脚始终为低?谢谢