Part Number: TMS320C6748

Hi Gary,

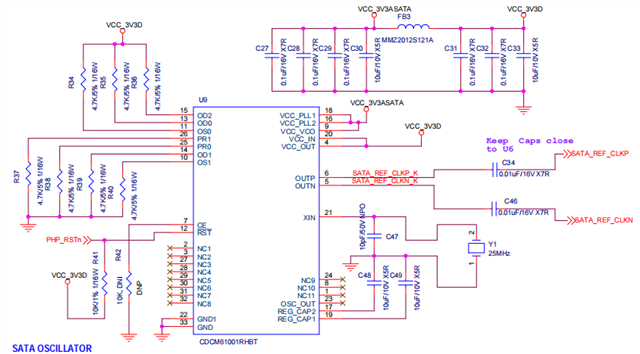

我们的板子使用C6748的sata接口外挂了一个msata盘,用了你们TI的CDCM61001RHBT这颗时钟发生器产生150MHz的LVDS时钟给sata接口使用,并且C6748外部晶振是24MHz;

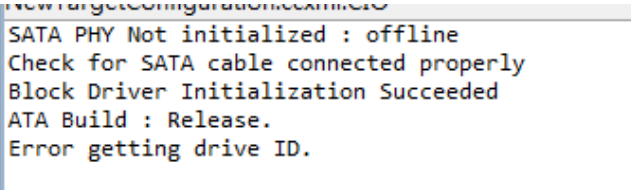

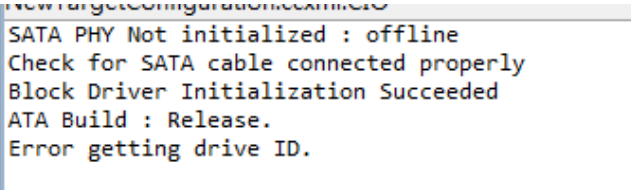

初始化的log如下,想问下这个大概率是什么问题,定位的方向在哪里,另外你们开发板上面的给sata接口的参考时钟是多少?谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320C6748

Hi Gary,

我们的板子使用C6748的sata接口外挂了一个msata盘,用了你们TI的CDCM61001RHBT这颗时钟发生器产生150MHz的LVDS时钟给sata接口使用,并且C6748外部晶振是24MHz;

初始化的log如下,想问下这个大概率是什么问题,定位的方向在哪里,另外你们开发板上面的给sata接口的参考时钟是多少?谢谢

您好,

可能是由于时钟配置错误或者SATA接口的初始化问题导致的。以下是一些可能的定位方向和解决建议:

1. 时钟配置问题:首先需要确认CDCM61001RHBT时钟发生器的配置是否正确,包括输入时钟的频率、输出时钟的频率、时钟分频等设置。确保150MHz的LVDS时钟被正确配置并连接到SATA接口。

2. SATA接口初始化问题:检查SATA接口的初始化代码,确保正确地配置了SATA控制器以适配150MHz的时钟频率。

3. 信号完整性问题:150MHz的LVDS时钟信号在传输过程中需要保证信号完整性,包括匹配阻抗、信号幅度、时序等。确保时钟信号的传输线路和连接都符合LVDS时钟信号的要求。

4. 参考时钟问题:你提到TI的CDCM61001RHBT产生的150MHz的LVDS时钟是基于C6748的外部晶振24MHz的。确保外部晶振的稳定性和精度,以及CDCM61001RHBT的配置与外部晶振的匹配。

Hi Gary,

看了一下你们的公板,和你确认几个问题:

1.你们的C6748的SATA接口是不是有bug,如果外挂一个sata 3.0的盘,不能正常的读写盘,你们的勘误表中不推荐使用C6748的SATA接口,是这样的吗?

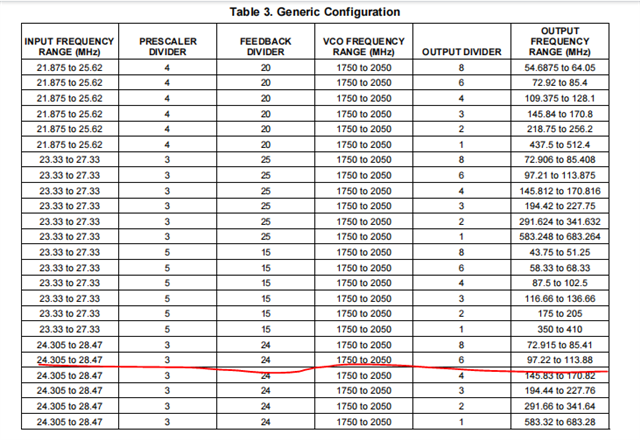

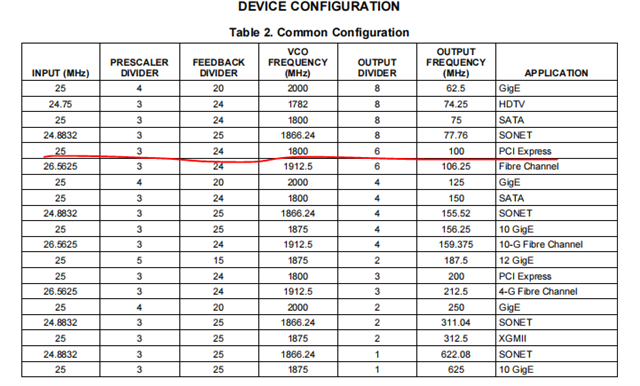

2.你们的公板,配置如下,OUTPUT DIVIDER=6 ,PRESCALER DIVIDER=3,FEEDBACK DIVIDER=24,output type=LVDS OSC_OUT off这样一来,CDCM61001RHBT是输出100MHz的LVDS差分时钟给SATA接口,所以你们的C6748接口到底是需要75MHz的时钟?还是150MHz的时钟?如下是你们的原理图和相应的CDCM61001RHBT的配置表: