Part Number: TMS320C6747

最近在用EMIFA的异步接口实现DSP与FPGA间的数据读写功能,但是通信速率有点慢,目前因硬件问题不考虑使用EDMA,因此主要采用时序优化来提升通信速率。

调试过程中遇到了以下几点问题,希望各位大佬指教指教:

问题1:两次联系读或写之间的延时问题

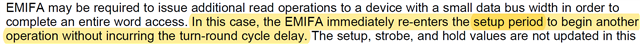

用户手册上有提到,当需要读写的数据大于数据总线宽度时,EMIFA会立即进入设置时期以继续读写,直至将所有的数据全部读写完毕。原文如下:

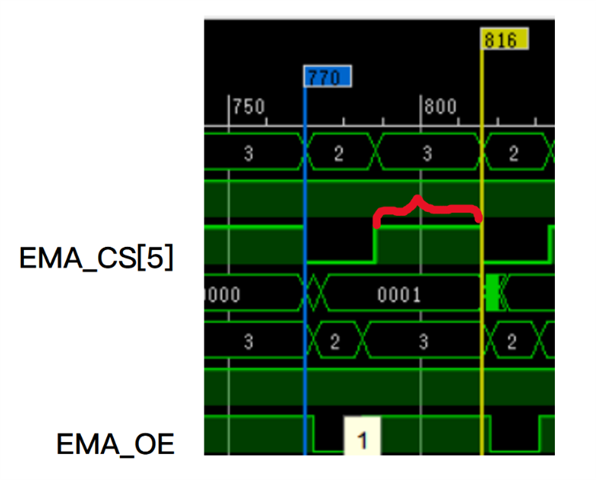

以读操作为例,EMIFA总线宽度为16bit,但是我要读160bit的数据,在调试过程中我发现,在读取完一个16bit数据后,系统并没有立即进入下一个Setup阶段,而是存在一定的延时,该延时约400ns,是制约我通信速率的主要原因。调试过程中的波形图如下(ila驱动时钟为100MHz):

请问各位大佬,这个时间可以通过配置某些参数来缩短吗?还是不可避免的?

问题2:读、写过程的Setup、Strobe和Hold的配置问题

为了缩短读写时间,我尝试修改了读写过程的Setup、Strobe和Hold时间,我发现,当我调整读过程中的Strobe时间时,两次相邻读操作的时间间隔也会响应的产生变化(如图):

(1)strobe为50ns时:

此时间隔为430ns。

此时间隔为430ns。

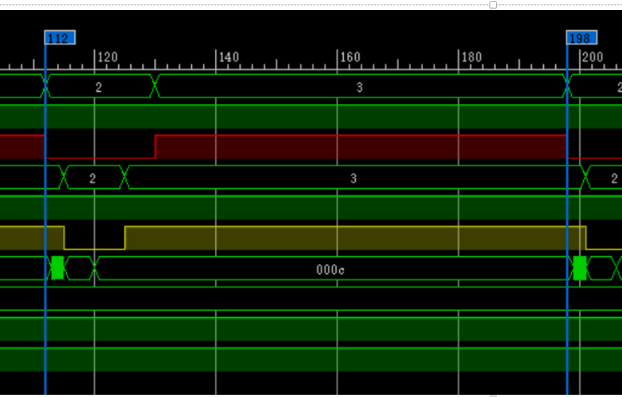

(2)strobe为50ns时:

此时间隔为460ns。

此时间隔为460ns。

但是在写的过程中,无论我如何修改参数,相邻两次写操作的时间间隔始终为200ns。

想知道为什么会有如此区别?

问题3:EMIFA时钟频率修改引发的问题

为了进一步提升读写速率,我将EMIFA的时钟输入由100MHz提升到了133MHz,在此情况下,DSP中测试得出的读、写耗费的主频时钟数确实有所减少,但是FPGA中的波形未收到明显影响,写的周期开始在200ns附件浮动,而读的周期仍旧为460ns,请问为什么会这样?另外,我的FPGA的时钟主频为100MHz,如果EMIFA的时钟提升到了133MHz,目前调试看来,双方读写不会出现错误的,但是是否会有隐患?