Part Number: AFE7955

Other Parts Discussed in Thread: AFE7950,

1、硬件设计:

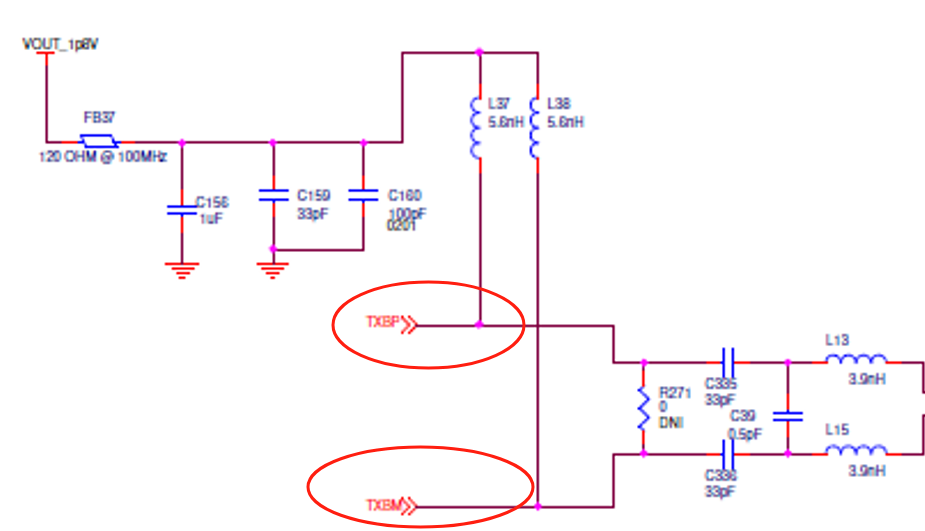

参考的AFE7950,但是对于DAC端的输出信号设计的阻抗为100欧,经过巴伦转换至单端信号的阻抗为50欧,其他的电路设计几乎与开发板一致。电路设计如下图,画圈处与DAC的输出端直连,该点无信号输出。

,2、软件设计:

通过初始化配置,满足设计要求。

希望TI技术支持能给一些指导建议,期待你的回复,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

要确认的是、客户是使用 FPGA 来对 AFE 进行编程、而不是使用 Latte 软件吗? 他们能否共享用于测试的启动文件?

在启动 AFE 时、它们是否会接收到任何 JESD 警报?

客户还可以参考以下文档来调试问题。

https://www.ti.com/lit/an/sbaa637/sbaa637.pdf

他们是否还可以确认正在检查 Tx 侧的一个启用的通道? 对于 AFE7955、只有2个可用的发送通道、即 Tx1和 TX3。

############## Read me ##############

#In HSDC Pro DAC tab, Select AFE79xx_1x2TX_44210; Data Rate = 491.52M

#In HSDC Pro ADC tab, Select AFE79xx_3x1RX_22210; Data Rate = 491.52M

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 # setup FPGA (TSW14J56) using HSDC Pro

############## Top Level ##############

sysParams.FRef = 368.75

sysParams.FadcRx = 2950

sysParams.FadcFb = 2950

sysParams.Fdac = 2950*4

sysParams.externalClockRx=False

sysParams.externalClockTx=False

#sysParams.ncoFreqMode = "1KHz"

#sysParams.enableDacInterleavedMode = False

#sysParams.rxJesdTxScr = [False,False,False,False]

#sysParams.fbJesdTxScr = [False,False]

#sysParams.jesdRxScr = [False,False]

############## Digital Chain ##############

##### RX #####

sysParams.ddcFactorRx = [2]*4 #DDC decimation factor for RX A, B, C and D

sysParams.rxNco0 = [[4800,4800]]*4 #Band0, Band1 for RXA

sysParams.rxEnable = [True,False,True,False]

##### FB #####

sysParams.fbEnable = [False,False]

sysParams.ddcFactorFb = [8]*2 #DDC decimation factor for FB 1 and 2

sysParams.fbNco0 = [4800,4800] #Band0 for FB1 and FB2

##### TX #####

#sysParams.txEnable = [False,True,False,True]

sysParams.ducFactorTx = [8]*4 #DUC lx 24 interpolation factor for TX A, B, C and D

sysParams.txNco0 = [[4800,4800]]*4 #Band0, Band1 for TXA

sysParams.txEnable = [True,False,True,False]

#for i in [0,1]:

# for j in [0,1]: #AFE.JESD.DACJESD[i].dacJesdConstantTestPatternValue(1,j,0,16384,0) # enable, channelNum, bandNum, Ival, Qval

############## JESD ##############

##### ADC-JESD #####

sysParams.jesdSystemMode= [3,3]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; rx -rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb -fb- fb -fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol= [0,0] # 0 - 8b/10b encoding; 2 - 64b/66b encoding

sysParams.LMFSHdRx = ["42220"]*4

# The 2nd and 4th are valid only for jesdSystemMode values in (0,2).

# For other modes, select 4 converter modes for 1st and 3rd.

sysParams.LMFSHdFb = ["42220"]*2

sysParams.rxJesdTxScr = [True,True,True,True]

sysParams.fbJesdTxScr = [True,True]

sysParams.rxJesdTxK = [16,16,16,16]

sysParams.fbJesdTxK = [16,16]

#sysParams.rxDataMux = [0,1,2,3,4,5,6,7]

#sysParams.jesdTxLaneMux = [0,1,4,5,2,3,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2T,

# this should be [[1,0,2,3],[5,4,6,7]]

##### DAC-JESD #####

sysParams.jesdRxProtocol= [0,0]

sysParams.LMFSHdTx = ["42220"]*4

#sysParams.txDataMux = [2,3,0,1,6,7,4,5]

#sysParams.txDataMux = [0,1,2,3,4,5,6,7]

#sysParams.jesdRxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2R

# this should be [[1,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd = [4, 4]

sysParams.jesdRxScr = [True,True,True,True]

sysParams.jesdRxK = [16,16,16,16]

##### JESD Common #####

sysParams.jesdABLvdsSync= 0

sysParams.jesdCDLvdsSync= 0

sysParams.syncLoopBack = True #JESD Sync signal is connected to FPGA

#sysParams.jesdLoopBackEn = True

sysParams.rxJesdTxSyncMux = [0]*4

sysParams.jesdRxSyncMux = [0]*4

#AFE.FPGA.dacTones['TXA_B0_SIG']=10

#AFE.FPGA.dacTones['TXB_B0_SIG']=10

#AFE.FPGA.dacTones['TXC_B0_SIG']=10

#AFE.FPGA.dacTones['TXD_B0_SIG']=10

############## GPIO ##############

sysParams.gpioMapping = {

'H8': 'ADC_SYNC0',

'H7': 'ADC_SYNC1',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'DAC_SYNC0',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

############## LMK Params ##############

#lmkParams.pllEn = False

lmkParams.pllEn = True

lmkParams.inputClk = 100 # Valid only when lmkParams.pllEn = False

lmkParams.lmkFrefClk = True

setupParams.fpgaRefClk = 368.75 # Should be equal to LaneRate/40 for TSW14J56

lmkParams.xtalFreq = 100

lmkParams.lmkVcoFreq = 2950

sysParams.RRFMode = 5

#-----------------------------------------------------------#

setupParams.skipLmk = False

AFE.initializeConfig()

lmkParams.sysrefFreq = AFE.systemStatus.sysrefFreq

lmkParams.lmkpulseSysrefMode = False

AFE.LMK.lmkConfig()

#--------------Initiates AFE79xx Bring-up--------------#

############## Logging ##############

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0xff #Modify to 0x1 to save register scequence to log file. Script takes more time to execute.

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

lmklogDumpInst=mLogDump.logDump(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1_LMK.txt")

lmklogDumpInst.logFormat=0xff

lmk.logClassInst = lmklogDumpInst

lmk.rawWriteLogEn=1

#for i in [0,1]:

# AFE.JESD.DACJESD[i].dacJesdSendRampTestPattern(15)

#for i in [0,1]:

# for j in [0,1]: #AFE.JESD.DACJESD[i].dacJesdConstantTestPatternValue(1,j,0,16384,0) # enable, channelNum, bandNum, Ival, Qval

device.delay_time = 0

#-------------------------------------------------------------------------------------------------#

setupParams.skipLmk = True

AFE.deviceBringup()

AFE.TOP.overrideTdd(5,0,5) # bit-wise; 4R,2F,4T

#AFE.TOP.overrideTddPins(1,0,1) # bit-wise; 4R,2F,4T