你好,

我这边按照手册通过SPI配置AWR2243,使能FrameStart后可以收到RF_ASYNC_EVENT_MSG1的Frame Trigger Ready以及Frame End的回复,但是 CSI接口上的CLK和line没有信号输出

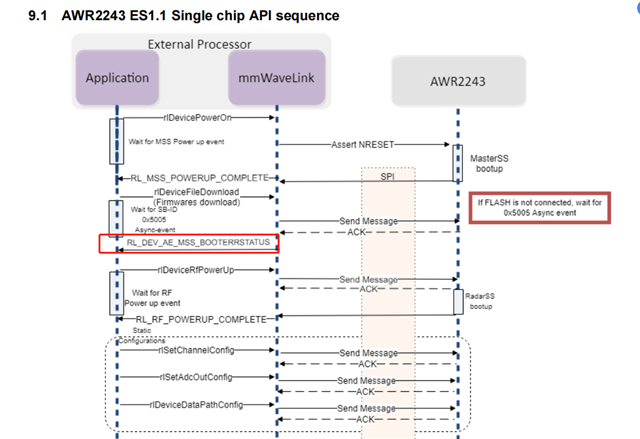

我的配置流程:

1. 控制AWR2243复位引脚,等待MSS_POWERUP_COMPLETE回复,回复状态为缺少MetaHearer

2. 通过SPI加载xwr22xx_metaImage.h文件里的固件数组,每一包发送都有ACK回复,发送完成后未有图中左边红框的MSS_BOOTERRSTATUS回复;下图右边的红框提示如果没有连接Flash才等0x5005事件,现在的设计上是通过QSPI连接了一片Flash的,所以是否不会有MSS_BOOTERRSTATUS的回复? 加载固件后怎么确定固件是否加载成功?

3. 使能RF PowerUp,接收到回复的数据为: ba dc cd ab 36 a0 22 00 0c 00 00 00 01 00 9a 5f 01 50 14 00 fb fe 3b 07 76 50 21 00 10 00 00 00 00 00 00 00 20 61

4. 配置Static_Conf_Set相关寄存器

a. AWR_RF_DEVICE_CFG_SB 配置ASYNC_EVENT_DIR为BSS TO HOST

配置MONITORING_ASYNC_EVENT_DIR为BSS TO HOST

使能FRAME_START_ASYNC_EVENT和FRAME_STOP_ASYNC_EVENT

使能INTER_BURST_POWER_SAVE

关闭WDT

ASYNC_EVENT_CRC设置为32bit

b. AWR_CHAN_CONF_SET_SB 使能4路RX和TX0

配置为单Chip模式

关闭FM_CW_CLKOUT_MASTER, FM_CW_SYNCOUT_MASTER, FM_CW_CLKOUT_SLAVE, FM_CW_SYNCOUT_SLAVE, INTLO_MASTER, INTFRC_MASTER

打开OSCCLKOUT(用于给外部FPGA做时钟源)

c. AWR_ADCOUT_CONF_SET_SB 配置adc为12bit,Reduse Full Scale Bits为0,仅要real

d. AWR_RF_RADAR_MISC_CTL_SB 全配置为0

5. DATA_PATH设置

a. AWR_DEV_RX_DATA_FORMAT_CONF_SB 按照需求配置了adc的数据格式

b. AWR_DEV_RX_DATA_PATH_CONF_SET_SB 配置为CSI接口模式

c. AWR_DEV_RX_DATA_PATH_CLK_SET_SB 配置为CLK_DDR模式,速率为150M

d. AWR_HIGHSPEEDINTFCLK_CONF_SET_SB 配置为300M

e. AWR_DEV_CSI2_CFG_SET_SB 按默认Lane0在Pos1,Lane1在Pos2,Lane2在Pos4, Lane3在Pos5, CLK在Pos3,所有线都设置为POL_PLUSMINUS; 使能LineStartEnd

6. 配置RF INIT,等待回复RF_AE_INITCALIBSTATUS_SB的数据为: ba dc cd ab 32 20 28 00 0c 04 00 00 01 00 98 db 04 10 18 00 fe 0f 00 80 fc 0f 00 00 23 00 00 00 3b 04 00 00 0f 00 00 00 c7 aa 9e 4d

7. 配置Profile信息,采样点为64;

8. 配置CHIRP_CONF_SET,绑定Profile0,ChirpStartIndex和ChirpEndIndex为0,仅设置1种chirp

9. 配置AWR_FRAME_CONF_SB, ChirpStartIndex和ChirpEndIndex为0; NumLoops为1; NumFrames为64

10. 配置AWR_DEV_FRAME_CONF_SB, NumChirps为64; HalfWordsPerChirp为64(采样点为64,只传输real)

11. 使能FrameStart,可以收到RF_ASYNC_EVENT_MSG1的Frame Trigger Ready,等待一会后再次收到Frame End的回复

按照上述步骤执行完后,CSI接口上CLK和Lane一直没有输出, 请问我可以从哪些方面排查此问题呢? 问题困扰几天了,期望得到回复,感谢